# RemembERR: Leveraging Microprocessor Errata for Design Testing and Validation

Flavien Solt, Patrick Jattke and Kaveh Razavi Computer Security Group, ETH Zürich

Abstract—Microprocessors are constantly increasing in complexity, but to remain competitive, their design and testing cycles must be kept as short as possible. This trend inevitably leads to design errors that eventually make their way into commercial products. Major microprocessor vendors such as Intel and AMD regularly publish and update errata documents describing these errata after their microprocessors are launched. The abundance of errata suggests the presence of significant gaps in the design testing of modern microprocessors.

We argue that while a specific erratum provides information about only a single issue, the aggregated information from the body of existing errata can shed light on existing design testing gaps. Unfortunately, errata documents are not systematically structured. We formalize that each erratum describes, in human language, a set of *triggers* that, when applied in specific *contexts*, cause certain *observations* that pertain to a particular bug. We present RemembERR, the first large-scale database of microprocessor errata collected among all Intel Core and AMD microprocessors since 2008, comprising 2,563 individual errata. Each RemembERR entry is annotated with triggers, contexts, and observations, extracted from the original erratum. To generalize these properties, we classify them on multiple levels of abstraction that describe the underlying causes and effects.

We then leverage RemembERR to study gaps in design testing by making the key observation that triggers are *conjunctive*, while observations are *disjunctive*: to detect a bug, it is necessary to apply *all* triggers and sufficient to observe only a *single* deviation. Based on this insight, one can rely on partial information about triggers across the entire corpus to draw consistent conclusions about the best design testing and validation strategies to cover the existing gaps. As a concrete example, our study shows that we need testing tools that exert power level transitions under MSR-determined configurations while operating custom features.

## I. INTRODUCTION

What are the bugs that we could not discover before we sent the microprocessor design for fabrication? This is probably the most important question that design test engineers repeatedly ask themselves. The question is not getting any easier to answer with the ever-increasing complexity of modern microprocessors [1]. Despite advances in design testing tools and techniques [2]–[23], we still see plenty of post-production bugs after new microprocessors are released, indicating that there exist gaps in design testing and validation. In this paper, we identify these gaps and propose concrete actions to cover them by leveraging a new classification based on errata reported by Intel and AMD.

**Design testing and validation.** Before a microprocessor is shipped to customers, it goes through a variety of testing and validation steps. In the early stages, a design simulation using random or human-driven inputs may reveal bugs [2], [16]. Once the design matures, formal verification techniques ensure the correctness of selected design parts [17]–[19], [24],

[25]. Finally, many bugs can only be found in post-silicon testing under real-world conditions [26]–[31]. These design testing and validation methods, unfortunately, do not scale to the complexity of today's microprocessor designs [16]. In the testing steps, the lingering question is whether the test cases are providing a sufficient coverage [32]–[34]. Similarly, expensive verification efforts should be targeted to those parts of the design where critical bugs are likely to lurk.

**Microprocessor errata.** In response to the discovery of bugs after production, microprocessors vendors regularly publish errata documents: human-readable documents containing a list of errata [15], [35]-[38]. The goal of publishing this list of defects is to document known bugs and to provide system designers with workaround guidance where appropriate. The organization of errata differs across vendors, but the structure of each erratum entry remains similar. Each erratum, from both Intel and AMD, includes a description with information about the conditions under which the bug occurs and a brief discussion of its *implications* once triggered. Furthermore, each entry includes information about the proposed workarounds and whether or not the bug has been fixed. While the individual erratum is useful for keeping track of a bug and informing users about it, we argue that grouping them reveals precious information that can guide future design testing and validation.

RemembERR. To extract the relevant information from the errata, we created RemembERR, a comprehensive, annotated database of all errata of Intel Core and AMD microprocessor families since 2008, with a total of 2,563 entries. Creating this database itself presented challenges since the errata are not machine-readable: (a) they lack an identical structure between documents, (b) they contain a significant number of errors such as duplicate entries in the same document, reused errata numbers, and erroneous Model Specific Register (MSR) numbers, and (c) a lack of classification and consistency in notations. To facilitate guiding testing and validation, we create a new classification of errata for RemembERR. We manually annotate each RemembERR entry with its necessary *triggers*, the *contexts* to which the bug applies, and the *observations* that can be made once the bug is triggered. We call this level the *concrete* level of our classification. Although useful, the concrete level can sometimes be too erratum-specific to generalize. For example, a particular offset inside a certain machine-specific register must be written to trigger a bug. To study causes and effects in an aggregate manner, we further classify and annotate RemembERR entries at two higher levels of abstraction, which we call the abstract and class levels.

Equipped with RemembERR, we then study trends to identify design testing gaps. We make a key observation that in almost

every erratum, trigger conditions are *conjunctive*, while contexts and observations are *disjunctive*. This means that to discover a bug, *all* triggers must be activated (e.g., a misaligned load that causes a page fault), in *any* of the applicable contexts (e.g., in user mode), and observing *any* behavior deviating from the expected behavior (e.g., a machine check exception) is sufficient to detect the bug. This powerful insight allows us to extract valuable information from aggregated errata, regardless of how vague each individual erratum may be on its triggers and/or observations (the contexts are usually clear). Importantly, this information about triggers, contexts, and observations is necessary for directing design testing and validation campaigns to discover bugs that are not currently missed by the existing tools and techniques.

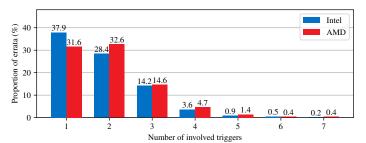

Our study shows that more than 40% of bugs are uncovered only when two distinct trigger types are combined. Moreover, most triggers do not interact with each other, while others seem to be closely related and together, they bring up new bugs. Exploiting these interactions is crucial to boost future design testing and validation of microprocessors and to keep up with their increasing complexity.

Contributions. We make the following contributions:

- We propose a new classification of design flaws based on necessary triggers, and sufficient contexts and observations.

- We create RemembERR, a comprehensive database created from 2,563 public errata across all 12 first generations of Intel Core and 13 current AMD microprocessor families.

- Using RemembERR, we study trends in post-production microprocessor bugs and develop testing and validation guidelines that relate triggers, contexts, and observations.

**Open sourcing.** We make the entire RemembERR database, including our annotations, publicly available so that researchers and design test engineers can draw conclusions specific to their goals and automate their tools.

## II. BACKGROUND

This section provides some brief background on existing hardware bug detection techniques (Section II-A) and errata documents (Section II-B).

#### A. Bug detection methods

We provide background on the three commonly used techniques for detecting hardware bugs [16]: simulation, formal methods, and silicon testing.

**Simulation.** Design simulation is a traditional testing technique that is already used early in the design's development cycle [16]. During a simulation, the design is given sequences of inputs. The outputs and the resulting state of the design are then compared against a golden model [12] or inspected manually [16], [39]. Modern simulators provide a rich set of features, such as undefined values (i.e., *don't care* values), signal injection, and various coverage metrics [40]–[42].

Testing with simulation has two major shortcomings. First, simulation-based testing is extremely slow. Therefore, it can process only a few inputs in a reasonable time, making it challenging to reach all possible system states. For example, the open-source CVA-6 64-bit RISC-V core requires four days to boot Linux in simulation [43]. We expect more complex CPUs, tailored towards high performance, to be even more complex by several orders of magnitude. Simulation becomes mostly ineffective for complex modern microprocessors without limiting the test cases to those effective in triggering bugs. Second, simulation cannot expose issues related to the physical design, such as timing violations, data loss after power gating [44], or interaction with real-world peripherals and memories. Emulation, in spite of being significantly faster, suffers from the latter shortcoming as well.

Formal methods. Unlike simulation, which may suffer from limited input coverage, formal verification methods aim to prove that certain properties always hold given some allowed inputs. This approach makes it possible to prove correctness for all expected inputs — achieving completeness. However, these powerful formal methods have three weaknesses. First, they typically do not scale to complex designs with many stateful elements [16], [45]–[47]. Therefore, a typical approach is to verify only selected design parts while modeling the rest [48]– [50]. Second, properties may be difficult to express formally, and there can exist many properties for complex designs [51], [52]. Third, properties related to power management or other physical effects may be difficult to reason about [44], [53]-[56]. As each property is proven exhaustively, quickly rendering verification time infeasible, the test and validation engineers must carefully decide which properties to prove.

**Silicon testing.** Complex bugs often escape traditional presilicon testing and validation [26]–[31], [57]. Therefore, silicon testing remains a crucial part of design validation, and takes up to 50% of the testing cost for commercial designs [58]. In contrast to simulation, silicon testing achieves far higher throughput, but it does not reach the completeness offered by formal methods. Furthermore, silicon testing makes the design's internals inaccessible.

### B. Errata

For each design generation (Intel) or family (AMD) of microprocessors, vendors typically provide a *specification update* document, also known as *errata*, for listing known bugs after a product has been shipped. When a customer observes that a microprocessor deviates from its original specification, they can look through the errata documents to verify whether it is a known bug. The errata also provide information on how to avoid triggering unwanted behavior. Notably, the bugs described in errata documents can no longer be fixed and remain for the lifetime of the affected microprocessors.

**Organization.** Following their intended purpose, errata documents produced by Intel and AMD are human-readable PDF documents listing the individual bugs. Each erratum has a *title*, a *description*, *implications*, *workarounds*, and a *status*

<sup>&</sup>lt;sup>1</sup>https://github.com/comsec-group/rememberr

ID: ADL001

Title: X87 FDP Value May be Saved Incorrectly

**Description:** Execution of the FSAVE, FNSAVE, FSTENV, or FNSTENV instructions in real-address mode or virtual-8086 mode may save an incorrect value for the x87 FDP (FPU data pointer). This erratum does not apply if the last non-control x87 instruction had an unmasked exception.

**Implications:** Software operating in real-address mode or virtual-8086 mode that depends on the FDP value for non-control x87 instructions without unmasked exceptions may not operate properly. Intel has not observed this erratum in any commercially available software.

**Workaround:** None identified. Software should use the FDP value saved by the listed instructions only when the most recent non-control x87 instruction incurred an unmasked exception.

Status: For the steppings affected, refer to the Summary Table of Changes.

## **Table II.** An erratum for AMD Zen 3 family.

**ID:** 1361

**Title:** Processor May Hang When Switching Between Instruction Cache and Op Cache.

**Description:** Under a highly specific and detailed set of internal timing conditions, running a program with a code footprint exceeding 32 KB may cause the processor to hang while switching between code regions that consistently miss the instruction cache and code regions contained within the Op Cache.

Implications: System may hang or reset.

Workaround: System software may contain the workaround for this erratum.

Status: No fix planned.

indicating whether a fix is available for current or future releases of the same CPU generation or family. Intel released separate erratum documents for the Mobile and Desktop version of its Core microprocessors until generation 5. After that, they released only one document per generation. AMD uses a single document per CPU family (i.e., per CPU microarchitecture).

**Errata examples.** We provide two recent errata examples. In Table I, we show the first erratum for Intel Core 12th generation CPUs, and in Table II, the most recent erratum for AMD Zen 3 family CPUs.

#### III. MOTIVATION: LEARN FROM THE PAST

The number of published errata has not significantly decreased over time, as we show in Section IV. Strikingly, we will show that some bugs require years to be reported, while similar bugs were already found in previous designs. These trends point to gaps in existing design testing and validation tools and techniques. A data-driven approach using the information contained in the errata can shed light on these gaps and provide directions for covering them.

Accessibility. Each erratum is specific to one bug in a particular design, complying with a certain Instruction Set Architecture (ISA). This makes deriving any valuable insights from a series of individual errata difficult. Further, it does not incite communities that build and verify other microprocessors to read and learn from known pitfalls and spots that require special testing focus. This is becoming increasingly more important as the complexity of community-driven microprocessors is progressively catching up with their proprietary and

closed-source counterparts [59]–[61]. By aggregating errata and building an annotated database, we intend to make this information more accessible than it currently is.

**Structure.** The way errata are structured is suitable for reading by an experienced human but is not optimized for automated data mining. A clear specification of what each field contains or implies is missing. The useful information is often spread across the title, description, and implication (and sometimes workaround) fields, with a high degree of redundancy. This observation calls for creating and maintaining an improved erratum structure, scheme and tooling support that would be more adapted for data mining and to rule out redundancy while remaining human-readable.

Guiding design testing and validation. In complex CPU designs, all testing and validation methods must be directed. Formal methods require knowing the bug type to target and prioritizing the parts of the design that are most susceptible. Furthermore, formal properties must be local and specific to minimize the impact of state explosions. For dynamic methods such as simulation and silicon testing, it is crucial to know which input signals to provide in which context and what effects to expect if a bug is triggered [39], [62]. In Section VI, we provide an in-depth discussion on how the annotated errata information can enhance existing validation methodologies.

For example, errata reveal that specific bugs require ongoing PCIe communication. Is connecting a PCIe device enough to discover all PCIe-related bugs? Looking at all the errata, we observe that some PCIe-related bugs require triggering a reset signal. Furthermore, how can we efficiently observe whether a bug was triggered? This knowledge of the interaction between different input types, contexts, and effects is crucial for maximizing a testing campaign's efficiency and efficacy.

## IV. REMEMBERR

In this section, we introduce RemembERR, an annotated database of 2,563 errata from AMD and Intel microprocessors. In Section IV-A, we first describe the scope and our methodology. Based on this (yet unannotated) database, we present essential observations about the current state of microprocessor errata in Section IV-B.

#### A. Methodology

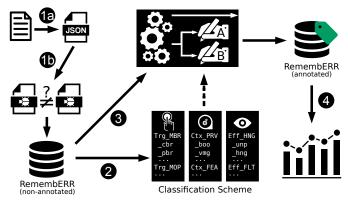

Figure 1 presents an overview of our methodology. Our approach can be summarized into four steps: 1a First, we acquired the latest errata documents from Intel and AMD, and 1b analyzed duplicate errata. This already allows us to make general observations about errata's current state (Section IV-B). 2 We then generalized the triggers, contexts, and observable effects to derive a universal classification scheme for errata (Section V-A). 3 Using automation, we classified a portion of the errata, and for the rest, we used four-eyes manual classification. The result is the annotated RemembERR database. 4 Lastly, we leveraged RemembERR to derive novel insights for filling the gaps in existing design testing and validation (Section V-B).

Fig. 1. Overview of our methodology.

**Table III.** Inspected errata documents. Left: Intel Core CPUs, right: AMD CPUs. (M): Mobile, (D): Desktop.

|       | Intel        |      | AMD    |            |  |

|-------|--------------|------|--------|------------|--|

| Gen.  | Reference    | Fam. | Models | Reference  |  |

| 1 (D) | 320836-037US | 10h  | 00-0F  | 41322-3.84 |  |

| 1 (M) | 322814-024US | 11h  | 00-0F  | 41788-3.00 |  |

| 2 (D) | 324643-037US | 12h  | 00-0F  | 44739-3.10 |  |

| 2 (M) | 324827-034US | 14h  | 00-0F  | 47534-3.18 |  |

| 3 (D) | 326766-022US | 15h  | 00-0F  | 48063-3.24 |  |

| 3 (M) | 326770-022US | 15h  | 10-1F  | 48931-3.08 |  |

| 4 (D) | 328899-039US | 15h  | 30-3F  | 51603-1.06 |  |

| 4 (M) | 328903-038US | 15h  | 70-7F  | 55370-3.00 |  |

| 5 (D) | 332381-023US | 16h  | 00-0F  | 51810-3.06 |  |

| 5 (M) | 330836-031US | 17h  | 00-0F  | 55449-1.12 |  |

| 6     | 332689-028US | 17h  | 30-3F  | 56323-0.78 |  |

| 7/8   | 334663-013US | 19h  | 00-0F  | 56683-1.04 |  |

| 8/9   | 337346-002US |      |        |            |  |

| 10    | 615213-010US |      |        |            |  |

| 11    | 634808-008US |      |        |            |  |

| 12    | 682436-004US |      |        |            |  |

**Examined documents.** We comprehensively examined all the errata documents listed in Table III. Vendors usually withdraw errata documents once the processor line is not supported anymore, which makes finding the errata documents not always straightforward. We scraped the web thoroughly and took the most recent findable document for each generation (Intel) or family (AMD). We examined all the errata from the Intel Core series and all the errata from AMD CPUs since 2008.

Errata in errata. Errata documents contain many errors themselves. Examples are two revisions pretending to have added the same erratum (affects 8 errata across 3 documents), some errata are never mentioned in the revision notes (affects 12 errata across 2 documents), the same name refers to two different errata (affects an erratum named AAJ143), there are missing or duplicate fields in errata (affects 7 errata across 4 documents), or there are errors in the MSR numbers (affects 3 errata across 3 documents). In rare cases, errata may be repeated inside the same errata document (affects 11 errata pairs across 6 documents). These errors are a clear indicator that the writing of errata is a manual process. Humans not only express errata in a human language, but they also seem to be

responsible for non-systematically (redundantly) distributing information across errata fields.

**Duplicates.** As we will show, it is common that two (or multiple) designs from the same vendor with different release dates are affected by the same erratum. RemembERR contains all the duplicates as often as they appear across documents. This provides useful information about bugs shared among generations or families. However, to allow filtering for unique entries, RemembERR features a keying mechanism that assigns a unique identifier to each cluster of identical errata.

AMD identifies errata across microprocessor families using a unique numeric identifier: two families are affected by the same erratum if both have an erratum with the same number in their corresponding errata document. This mechanism protects against intra-document duplicates. Besides different errata numbers, some cases are indistinguishable given the limited information in the errata's fields. For example, errata no. 1327 and no. 1329 only differ in their suggested workaround but may originate from distinct root causes. *In total, we collected 506 errata from AMD, of which 385 are unique.*

Intel errata documents do not provide a simple way to identify duplicates across generations. Instead, we base our duplicate detection on the errata titles. As a first step, we marked all errata with the same title as duplicates. Extensive manual inspection of all the candidate duplicates shows that when the titles are (nearly) identical, all other fields are identical as well. Except for minor phrasing variations or slightly different levels of detail. As a second step, we manually analyzed remaining errata that have not been marked yet as duplicates, sorted by decreasing title similarity, given that title similarity is a strong indicator of potential duplicates. We could manually identify 29 pairs as duplicates. In total, we collected 2,057 errata for Intel, of which 743 are unique.

Because Intel and AMD use different identifiers for their errata, it is difficult to determine whether a bug is common between products of these two vendors; at least, we could not find any occurrence giving strong evidence. Arguably, Intel and AMD designs are proprietary; hence they might not share hardware blocks. It is, hence, unlikely for identical bug instances to occur across vendors.

## B. Observations

The data gathered in RemembERR allows us to make several novel observations about the current state of errata.

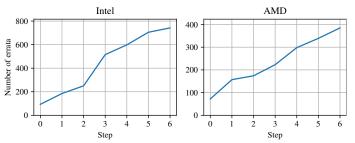

1) Timeline: We first analyze the number of reported bugs accumulated over time. Unfortunately, bug discoveries are not timestamped; hence, we approximate the timestamp of each erratum by identifying in which revision of the errata document it first appeared. We then use the errata document's release or update date to approximate the timestamp.

In some cases, the revision summary does not indicate in which revision a certain erratum was added. Fortunately, errata are sequentially numbered. Hence, we can approximate the date by assuming that the subsequent erratum was added simultaneously. In rare cases, we observed contradicting dates: revision logs falsely pretend that the same erratum was added

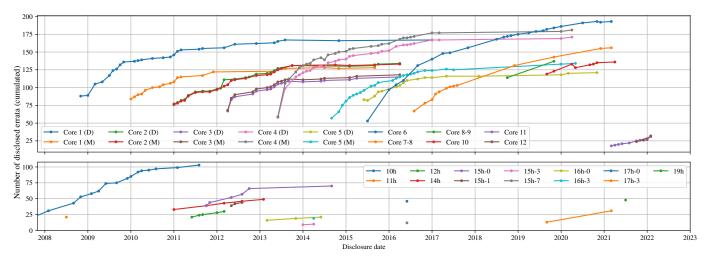

**Fig. 2.** Disclosure dates of Intel Core errata (top) and AMD CPU errata (bottom). The y-axis represents the cumulative number of disclosed errata. The data point represents the errata's release date.

in two consecutive revisions. In this case, we consider the date of the earlier of the two revisions as the correct one.

Figure 2 shows the cumulative growth of errata over time, where duplicate entries are counted individually. We observe that Intel updates its errata documents significantly more frequently than AMD. Desktop and mobile processors released at close dates have very similar curves, for example, Intel Core 2, 3, and 4 during the year 2013. This may suggest that the same bugs tend to affect multiple generations. In Section IV-B2, we study this bug *transmission effect* across design generations in more detail.

Figure 2 further demonstrates that vendors keep introducing new bugs into their products. While the latest microarchitectures seem to be less affected, it is likely that many bugs have not yet been discovered or reported.

(O1) Observation. The number of reported errata does not significantly decrease over time with new designs.

All cumulative curves tend to be concave. The more time passes, the fewer bugs are found in a given period. In most older designs, the curve stagnates towards the end, where only very few new bugs are discovered after many years from the initial release of the CPU, especially for Intel Core designs. This observation confirms the intuition that finding new bugs in a design becomes increasingly more difficult or that older designs are not as rigorously tested anymore compared to newer designs.

(O2) Observation. The increase in errata for a given design is usually concave.

2) Heredity: It is known from well-studied bugs such as Meltdown [63], Foreshadow [64], RIDL [64] and ZombieLoad [65], that different designs may suffer from exactly the same bug. One cause for this phenomenon may be the reuse of microarchitectural blocks across design generations. We study this phenomenon to provide an answer to the questions: (a) How

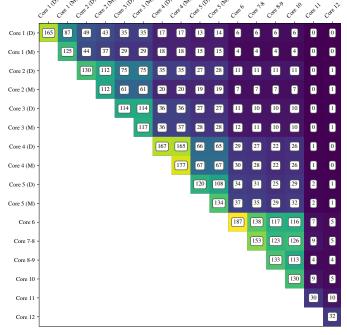

**Fig. 3.** Bug heredity: number of common bugs across Intel microprocessor generations.

often are bugs transmitted across generations or families? (b) Are transmitted bugs rediscovered multiple times?

**Transmission.** By definition, distinct AMD families have distinct microarchitectures. Our data corroborates that, as we find fewer shared errata between AMD families, compared to Intel Core generations. Furthermore, AMD provides limited chronological information, as depicted in Figure 2. Hence, we focus this part of our study on Intel errata.

Figure 3 shows the number of identical errata between pairs of Intel errata documents. We can observe that Desktop and mobile processors share the vast majority of bugs, matching our

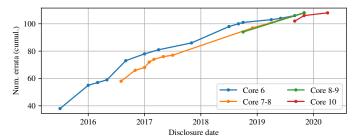

**Fig. 4.** Disclosure dates of Intel Core errata for bugs that are shared by all Intel Core generations from 6 to 10.

observation of similar curves in Section IV-B1. The processors that share a substantial part of their microarchitecture are salient in this diagram, such as Intel Core generations 6 to 10. Note that if a security bug is discovered only after multiple generations, an attacker could have exploited it for years without being uncovered. Therefore, the duration between bug introduction and discovery is not a suitable proxy for estimating criticality, especially regarding security. In Figure 3, long non-zero horizontal lines indicate long-lasting bugs. 6 bugs stayed from Core 1 to Core 10, and one erratum from Core 2 was still identified 11 generations later, more than 10 years after its initial discovery.

**(O3) Observation.** Bugs are often shared between generations of microprocessors. Shared bugs may stay for up to 11 generations.

**Rediscovery.** We conducted a further study to answer the question: from errata shared between microprocessors, which proportion was already reported in an earlier generation at the time of release?

Figure 4 shows the reporting date for the 104 bugs shared by all Intel Core generations from 6 to 10. This set of bugs corresponds to a salient region of common bugs in Figure 3. The first data point corresponds to the release date of each generation. Clearly, most of the shared design errors were known *before* the release of the subsequent generation, some even many years before.

This raises the question of where bugs are first discovered: in older designs and then confirmed on more recent ones (forward), or are they usually first found on more recent designs and then confirmed on older ones (backward)? While Figure 4 provides a qualitative insight, to answer this question, we define a forward-latent erratum as an erratum that was reported in one design and (strictly) later reported in a later design. Similarly, we say that an erratum is backward-latent if it was reported in a design (strictly) before being reported in an earlier design.

Figure 5 shows the forward-latent and backward-latent errata for Intel Core CPUs (again, the AMD errata documents lack sufficient chronological information for such an analysis). The salient portion of backward-latent errata around the year 2015 *may* represent a period at Intel where less resource was allocated to testing older CPU generations, for example, to prepare for the release of the Skylake microarchitecture.

**Fig. 5.** Forward-latent and backward-latent errata among Intel Core generations.

The increasing forward-latent numbers typically denote cores sequences with similar microarchitectures, where a bug has not been fixed, although it was known before the official CPU release. The number of forward-latent errata has always tended to increase, and this trend has accelerated since 2015. Note that these curves, for the time interval displayed here, may increase in the future with the rediscovery of more errata in existing or future Intel Core generations.

These results suggest that either the test and validation cycles are very long (in order of many years), making it difficult to react to newly discovered bugs during this phase, or these bugs are difficult to mitigate without fundamentally changing the microarchitecture.

**(O4) Observation.** Most of the design flaws that are shared between generations were already known before releasing the subsequent generation.

Observation *O4* indicates a correlation between long CPU development cycles and the difficulty of finding complex bugs.

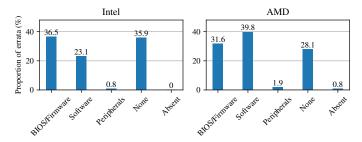

3) Workarounds: The vendors propose different workaround types, depending on where the workaround should be applied, i.e., which actor should (not) perform a specific action to ensure proper functionality. Based on this, we classify the workarounds into five categories: BIOS, software, peripherals, absent, and None. The category absent indicates existing workarounds without any specific information, such as "Contact [...] for information on a BIOS update." Instead of absent, whenever possible, we classify the workaround into a specific category even if the exact information is missing. Vendors use an additional category documentation fixes to describe originally intended behavior that was wrongly documented. This category is negligible in size as it represents less than 0.5% of the total number of errata.

We summarize our results in Figure 6, where identical errata are merged. The errata that can be mitigated in the BIOS are arguably the least critical, as long as the mitigation does not substantially affect performance or security. Errata requiring conditions in the peripherals or the software are more challenging to mitigate due to the plethora of legacy hardware and software. In total, 28.9% (AMD) and 35.9% (Intel) of all unique errata do not have any suggested workaround at all.

Fig. 6. Suggested workarounds of errata by category.

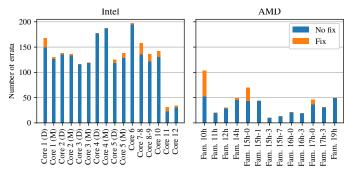

Fig. 7. Proportion of fixed vs. unfixed bugs.

**(O5) Observation.** A substantial number of errata do not have any suggested workaround.

As we discuss soon, this is not because bugs were fixed but because most bugs are deeply rooted in the design, limiting possible workarounds.

4) Fixes: In some cases, the vendors fix the root cause of a bug, as indicated explicitly in dedicated parts of the errata documents (in dedicated tables or in a status field). Fixes are distinct from workarounds as the former rules out the bug from the design completely, while the latter dynamically aims at preventing the bug from interfering with proper design functionality. Fixes may require a re-spin of the processor, which is an update of the CPU's design masks. We could not find any requirements driving the decision to fix a bug rather than proposing a workaround. Most likely, the decision is made based on the bug's criticality by considering functionality or security impact, and also the complexity of fixing the bug.

Figure 7 shows the number of bugs that are fixed in different designs. Clearly, the vast majority of bugs are never fixed. For Intel CPUs, there has been a weak trend over the last few generations toward fixing bugs.

(O6) Observation. Bugs are rarely fixed.

## V. CLASSIFICATION

This section introduces an errata classification scheme based on triggers, contexts, and effects. We start by describing the methodology we applied to design our classification scheme in Section V-A, after which we explain the classification scheme's categories. Using the classified data, we present new insights about bugs based on our classification results in Section V-B.

## A. Categories

A crucial part of our classification is the definition of concrete categories. We first made an exploratory pass over the errata documents to determine appropriate categories for triggers, contexts, and effects. To make the classification useful for our intended purpose, we require our concrete categories to be

- (a) *unambiguous*: a category should clearly be distinctive from other categories to improve our classification's reliability,

- (b) *usable*: categories should be helpful to guide the design testing process,

- (c) and *self-explanatory*: a one-sentence description should be sufficient to understand the category.

For instance, requiring a reset signal to observe faulty behavior is an unambiguous trigger (i.e., unlikely to be misclassified or misunderstood). It is a usable trigger because it is necessary to trigger observable behavior, and it is self-explanatory. If reset signals are not needed to find some bugs of interest, we should apply more relevant, directed test cases to increase effectiveness and close design testing gaps.

1) Classification methodology: In the following, we describe our systematic approach for designing our errata classification scheme. After that, we explain how we efficiently classified the errata consistently and reliably.

**Goal.** We designed a hierarchical classification scheme that allows us to seamlessly switch between different levels of abstraction. These abstraction levels are crucial for making the necessary observations and recommendations for improving design testing and validation. If the recommendations are too precise, methods cannot easily generalize the insights when looking for new bugs. If they are too abstract, however, then limited guidance will hamper efficiency and coverage.

Our classification scheme is composed of three levels: the concrete level, the abstract level, and the class level. We explain them for the example of triggers. First, the *concrete* level represents the exact action that is described in the erratum. For example, "the core resumes from the C6 power state" is an action described at the *concrete* level. Second, the *abstract* level represents a slightly higher level of abstraction. As an example, a transition between core power states is an action described at the abstract layer. The abstract level is crucial since design testing and validation tools must achieve generality to maximize coverage. In the example before, considering only transitions from the core C6 power state may not catch unknown bugs that only manifest when transitioning from other power states. Finally, the *class* level represents the highest level of abstraction; in our example, power management is the representation of the action at the class level. This last level of abstraction provides even more generality, contributes to better readability and allows us to make more general conclusions about the bugs triggered by a particular trigger class.

**Methodology.** We define the categories for triggers, contexts, and observable effects in an iterative way. We process all unique errata to extract *concrete* triggers, contexts, and observable effects. For each of them, we check if we already have a corresponding *abstract* category. If so, we then label the erratum

**Fig. 8.** Number of errata per errata classification discussion step.

with this abstract category; otherwise, we create a new abstract category, and we check if we have a corresponding class category. If a corresponding class category exists, we add the new abstract category to the existing class category; otherwise, we create a new class category and attach the new abstract category to it. We provide a detailed overview of class and abstract categories in Tables IV to VI.

RemembERR is a cross-ISA database as typically, only items (i.e., triggers, contexts, or effects) at the *concrete* level may be ISA-specific. Therefore, RemembERR can naturally be extended with errata from designs implementing other ISAs (e.g., POWER, ARM).

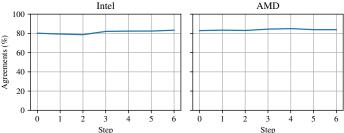

Four-eyes classification. Some errata contain expressions that are specific enough to be classified automatically using regular expressions into some categories, but many errata-category pairs require manual analysis for classification. Besides being time-consuming, manually extracting and annotating such an immense database of complex items is error-prone. To significantly improve the reliability of our results, two of the researchers involved in this work independently classified the errata. After completing the classification, they discussed and resolved each mismatch individually. To improve the classification and clarify our understanding of the categories, the discussions were made iteratively in seven successive steps for each design, using the same method but with the next batch of individually classified errata. Figure 8 shows the cumulative number of errata in each classification step. Figure 9 shows the evolution of the agreement of the decisions of the two humans. Note that, since the AMD errata were classified after the Intel errata, the data provided in Figure 9 is chronological. There are multiple reasons for mismatches, notably (i) human errors as classification is a tedious, long, and difficult process; (ii) imprecise description of the trigger, contexts, or effects in errata, leaving room for interpretation; and (iii) ambiguous classification categories. We note that the agreement percentage is generally above 80%.

**Software-assisted classification.** The cumulative number of categories for triggers, contexts, and observable effects is large: in total, we defined 60 categories. First, we merge identical unique errata in the decision-making process, resulting in 1,128 remaining errata. This still amounts to  $1128 \times 60 = 67,680$  classification decisions per human, even without considering the discussions for mismatches yet. We measured a typical

**Fig. 9.** Percentage of human-classified errata-category pairs classified identically by both humans before the discussion.

average duration of 30 seconds per classification decision, which amounts to more than 560 hours of high-focus work per human merely for the individual classification part.

Fortunately, some classes can be automatically filtered out as irrelevant for a given errata, given the text describing it. Some others can be automatically said to be clearly relevant to an erratum. With conservative filtering based on regular expressions, we could reduce the number of decisions to 2,064 per human in the individual phase. These remaining decisions are difficult to make automatically and reliably. For example, if a reset signal is a trigger or an effect in an erratum based on its description. For guiding the human-based classification, we designed a syntax highlighting engine with regular expressions to emphasize parts of the errata descriptions relevant to a given category. With this tool's assistance, we could reduce the amount of pure classification work and discussion to approximately 30 hours per human in total. We release all code along with the RemembERR database and envision that such computer-assisted classification tools will encourage further contributions to errata classification.

2) Triggers: Inputs that cause an exceptional observable effect are often not clearly stated or unspecified. At first sight, this renders the majority of errata unusable as they cannot easily be reproduced. However, we tackle this major challenge by designing a trigger classification scheme based on conditions that are *necessary* to cause an observable effect. Effectively, this means we define the required conditions under which suitable inputs can trigger a certain bug. This new classification method comes with several benefits. First, it allows deriving valuable insights even if only a limited amount of information is available. This makes our scheme especially useful for newer microprocessors or ISAs where fewer errata are available. Second, the categories we defined are largely independent and not exclusive, which allows for a simple estimation of a bug's complexity: the more necessary conditions are involved, the more complex the bug is to trigger. Furthermore, this classification scheme can easily be augmented in the future with new trigger classes, if needed.

In Table IV, we show all the categories for trigger that we defined on the *abstract* and *class* levels. We write *class* descriptors as the concatenation of two elements: (i) a prefix determining whether it refers to a trigger, context, or effect, and (ii) a suffix determining the *class*, given the prefix. For example,

**Table IV.** Classification of triggers.

| Trg_MBR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          | 86                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------|

| —pbr         page boundary.           —mbr         memory map boundary such as canonical.           Trg_MOP         a memory operation involving           —mmp         an interact. with a memory-mapped element.           — _atp         a condition on segment modes.           — _ptw         a condition on segment modes.           — _ptw         a core page table walk.           — _ptw         a core page table walk.           — _ptw         a condition on segment modes.           — _spet translation on nested page tables.           — _spet translation on nested page tables.           — _tmr         a speculative memory operation.           Trg_FELT         related to exceptions and faults           — _tmr         a timer event.           — _mca         a machine check exception.           — _tmr         a timer event.           — _wrett         a transition between hypervisor and guest.      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Trg_MBR                  | a data operation on a                     |

| —pbr         page boundary.           —mbr         memory map boundary such as canonical.           Trg_MOP         a memory operation involving           —mmp         an interact. with a memory-mapped element.           — _atp         a condition on segment modes.           — _ptw         a condition on segment modes.           — _ptw         a core page table walk.           — _ptw         a core page table walk.           — _ptw         a condition on segment modes.           — _spet translation on nested page tables.           — _spet translation on nested page tables.           — _tmr         a speculative memory operation.           Trg_FELT         related to exceptions and faults           — _tmr         a timer event.           — _mca         a machine check exception.           — _tmr         a timer event.           — _wrett         a transition between hypervisor and guest.      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | cbr                      | cache line boundary.                      |

| Trg_MOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | pbr                      |                                           |

| Trg_MOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          | memory map boundary such as canonical.    |

| mmp an interact. with a memory-mapped elementatp an atomic/transactional memory operationseg a condition on segment modesptw a core page table walknst translation on nested page tables fltc flushing some cache line or TLBspe a speculative memory operation.  Trg_FLT related to exceptions and faultsovf a counter overflowtmr a timer eventmca a machine check exceptionill an illegal instruction.  Trg_PRV related to privilege transitionsret a resume from System Management or OS modevmt a transition between hypervisor and guest.  Trg_CFG related to dynamic configurationpag a paging mechanism interactionwrg a configuration register interaction.  Trg_POW related to power statespwc a transition between power statestht a change in thermal or power supply conditions, or throttling.  Trg_EXT related to external inputsrst a (cold or warm) resetpci an interaction with PCIeusb an interaction with PCIeusb an interaction with USBram a specific DRAM configurationbus system bus (HyperTransport, QPI, etc.).  Trg_FEA related to featuresfpu floating-point instructionsdbg debug features such as breakpointscid design identification (CPUID reports)mon monitoring (MONITOR and MWAIT)tra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          |                                           |

| an atomic/transactional memory operation.  fen a memory fence or a serializing instruction.  a condition on segment modes.  a core page table walk.  Itanslation on nested page tables.  flushing some cache line or TLB.  a speculative memory operation.  Italian a counter overflow.  a timer event.  maca a machine check exception.  ill an illegal instruction.  Italian a resume from System Management or OS mode.  mach a paging mechanism interaction.  a virtual machine configuration interaction.  a virtual machine configuration interaction.  a virtual machine configuration interaction.  mach a resume from System Management or OS mode.  mach a paging mechanism interaction.  mach a paging mechanism interaction.  mach a virtual machine configuration interaction.  mach a paging mechanism interaction.  mach a paging mechanism interaction.  mach a paging mechanism interaction.  mach interaction register interaction.  mach interaction register interaction.  mach interaction interaction.  mach interaction.  mach interaction.  mach interaction.  mach interaction.  mach interaction.  mach interactio |                          | <u> </u>                                  |

| fen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                          |                                           |

| seg a condition on segment modesptw a core page table walknst translation on nested page tablesflc flushing some cache line or TLBspe a speculative memory operation.  Trg_FLT related to exceptions and faultsovf a counter overflowtmr a timer eventmca a machine check exceptionill an illegal instruction.  Trg_PRV related to privilege transitionsret a resume from System Management or OS modevmt a transition between hypervisor and guest.  Trg_CFG related to dynamic configurationpag a paging mechanism interactionwrg a configuration register interaction.  Trg_POW related to power statespwc a transition between power statestht a change in thermal or power supply conditions, or throttling.  Trg_EXT related to external inputsrst a (cold or warm) resetpci an interaction with PCIeusb an interaction with USBram a specific DRAM configurationiom an access through the IOMMUbus system bus (HyperTransport, QPI, etc.).  Trg_FEA related to featurescid debug features such as breakpointscid design identification (CPUID reports)mon monitoring (MONITOR and MWAIT)tra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                          |                                           |

| ptw a core page table walknst translation on nested page tablesflc flushing some cache line or TLBspe a speculative memory operation.  Trg_FLT related to exceptions and faultsovf a counter overflowtmr a timer eventmca a machine check exceptionill an illegal instruction.  Trg_PRV related to privilege transitionsret a resume from System Management or OS modevmt a transition between hypervisor and guest.  Trg_CFG related to dynamic configurationpag a paging mechanism interactionwrg a configuration register interaction.  Trg_POW related to power statespwc a transition between power statestht a change in thermal or power supply conditions, or throttling.  Trg_EXT related to external inputsrst a (cold or warm) resetpci an interaction with PCIeusb an interaction with PCIeusb an interaction with USBram a specific DRAM configurationiom an access through the IOMMUbus system bus (HyperTransport, QPI, etc.).  Trg_FEA related to featuresfpu floating-point instructionsdbg debug features such as breakpointscid design identification (CPUID reports)mon monitoring (MONITOR and MWAIT)tra tracing features.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |                                           |

| nst translation on nested page tablesflc flushing some cache line or TLBspe a speculative memory operation.  Trg_FLT related to exceptions and faultsovf a counter overflowtmr a timer eventmca a machine check exceptionill an illegal instruction.  Trg_PRV related to privilege transitionsret a resume from System Management or OS modevmt a transition between hypervisor and guest.  Trg_CFG related to dynamic configurationpag a paging mechanism interactionwrg a configuration register interaction.  Trg_POW related to power statespwc a transition between power statespwc a transition between power supply conditions, or throttling.  Trg_EXT related to external inputsrst a (cold or warm) resetpci an interaction with PCIeusb an interaction with USBram a specific DRAM configurationiom an access through the IOMMUbus system bus (HyperTransport, QPI, etc.).  Trg_FEA related to featuresfpu floating-point instructions. debug features such as breakpointscid design identification (CPUID reports)mon monitoring (MONITOR and MWAIT)tra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                          |                                           |

| flc   flushing some cache line or TLB.  spe   a speculative memory operation.  Trg_FLT   related to exceptions and faultsovf   a counter overflow.  tmr   a timer event.  mca   a machine check exception.  ill   an illegal instruction.  Trg_PRV   related to privilege transitions  ret   a resume from System Management or OS mode.  vmt   a transition between hypervisor and guest.  Trg_CFG   related to dynamic configuration  pag   a paging mechanism interaction.  wrg   a virtual machine configuration interaction.  wrg   a transition between power states  pwc   a transition between power states.  tht   a change in thermal or power supply conditions, or throttling.  Trg_EXT   related to external inputs  rst   a (cold or warm) reset.  pci   an interaction with PCIe.  usb   an interaction with USB.  ram   a specific DRAM configuration.  iom   an access through the IOMMU.  bus   system bus (HyperTransport, QPI, etc.).  Trg_FEA   related to features  fpu   floating-point instructions.  dbg   design identification (CPUID reports).  mon   monitoring (MONITOR and MWAIT).  tra   tracing features.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _                        |                                           |

| Trg_FLT related to exceptions and faults ovf a counter overflowtmr a timer eventmca a machine check exceptionill an illegal instruction.  Trg_PRV related to privilege transitionsret a resume from System Management or OS modevmt a transition between hypervisor and guest.  Trg_CFG related to dynamic configurationpag a paging mechanism interactionvmc a virtual machine configuration interactionwrg a configuration register interaction.  Trg_POW related to power statespwc a transition between power statestht a change in thermal or power supply conditions, or throttling.  Trg_EXT related to external inputsrst a (cold or warm) resetpci an interaction with PCIeusb an interaction with PCIeusb an interaction with PCIeiom an access through the IOMMUbus system bus (HyperTransport, QPI, etc.).  Trg_FEA related to featuresfpu floating-point instructions. debug features such as breakpoints. design identification (CPUID reports). mon monitoring (MONITOR and MWAIT)tra tracing features.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          |                                           |

| Trg_FLT related to exceptions and faults ovf a counter overflowtmr a timer eventmca a machine check exceptionill an illegal instruction.  Trg_PRV related to privilege transitions ret a resume from System Management or OS modevmt a transition between hypervisor and guest.  Trg_CFG related to dynamic configurationpag a paging mechanism interactionvmc a virtual machine configuration interactionwrg a configuration register interaction.  Trg_POW related to power statespwc a transition between power statestht a change in thermal or power supply conditions, or throttling.  Trg_EXT related to external inputspci an interaction with PCIeusb an interaction with PSBram a specific DRAM configurationiom an access through the IOMMUbus system bus (HyperTransport, QPI, etc.).  Trg_FEA related to featuresfpu floating-point instructions. debug features such as breakpointscid design identification (CPUID reports)mon monitoring (MONITOR and MWAIT)tra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          | •                                         |

| ovf a counter overflowtmr a timer eventmca a machine check exceptionill an illegal instruction.  Trg_PRV related to privilege transitionsret a resume from System Management or OS modevmt a transition between hypervisor and guest.  Trg_CFG related to dynamic configurationpag a paging mechanism interactionvmc a virtual machine configuration interactionwrg a configuration register interaction.  Trg_POW related to power statespwc a transition between power statestht a change in thermal or power supply conditions, or throttling.  Trg_EXT related to external inputsrst a (cold or warm) resetpci an interaction with PCIeusb an interaction with USBram a specific DRAM configurationiom an access through the IOMMUbus system bus (HyperTransport, QPI, etc.).  Trg_FEA related to featuresfpu floating-point instructions. debug features such as breakpointscid design identification (CPUID reports)mon monitoring (MONITOR and MWAIT)tra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | spe                      | a speculative memory operation.           |

| a timer event.  —mca a machine check exception.  —ill1 an illegal instruction.  Trg_PRV related to privilege transitions  —ret a resume from System Management or OS mode.  —vmt a transition between hypervisor and guest.  Trg_CFG related to dynamic configuration  —pag a paging mechanism interaction.  —vmc a virtual machine configuration interaction.  —wrg a configuration register interaction.  Trg_POW related to power states  —pwc a transition between power states.  —tht a change in thermal or power supply conditions, or throttling.  Trg_EXT related to external inputs  —rst a (cold or warm) reset.  —pci an interaction with PCIe.  —usb an interaction with USB.  —ram a specific DRAM configuration.  —iom an access through the IOMMU.  —bus system bus (HyperTransport, QPI, etc.).  Trg_FEA related to features  —fpu floating-point instructions.  debug features such as breakpoints.  —cid design identification (CPUID reports).  —mon monitoring (MONITOR and MWAIT).  —tra tracing features.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Trg_FLT                  | related to exceptions and faults          |

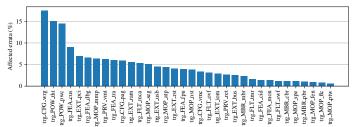

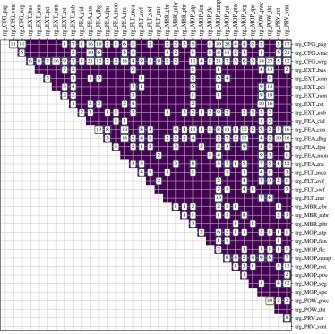

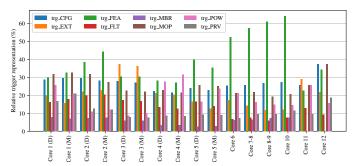

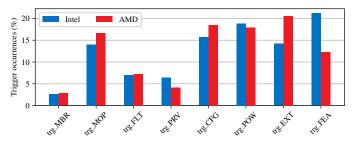

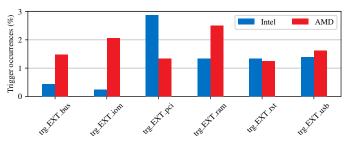

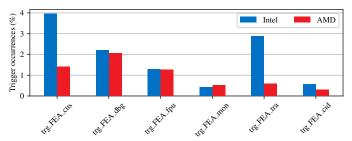

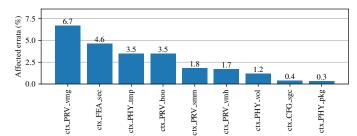

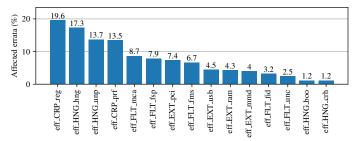

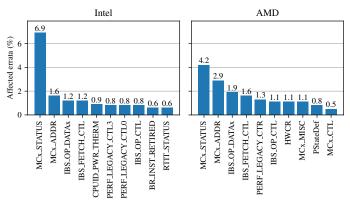

| a machine check exception. ill an illegal instruction.  Trg_PRV related to privilege transitions ret a resume from System Management or OS mode. vmt a transition between hypervisor and guest.  Trg_CFG related to dynamic configuration pag a paging mechanism interaction. vmc a virtual machine configuration interaction. wrg a configuration register interaction.  Trg_POW related to power states pwc a transition between power states. tht a change in thermal or power supply conditions, or throttling.  Trg_EXT related to external inputs rst a (cold or warm) reset. pci an interaction with PCIe. usb an interaction with USB. ram a specific DRAM configuration. iom an access through the IOMMU. bus system bus (HyperTransport, QPI, etc.).  Trg_FEA related to features fpu floating-point instructions.  debug features such as breakpoints. cid design identification (CPUID reports).  monitoring (MONITOR and MWAIT). tra tracing features.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ovf                      | a counter overflow.                       |