# Phoenix: Rowhammer Attacks on DDR5 with Self-Correcting Synchronization

Diego Meyer<sup>†</sup> *ETH Zurich*

Patrick Jattke<sup>†</sup> *ETH Zurich*

Michele Marazzi

ETH Zurich

Salman Qazi Google Daniel Moghimi *Google*

Kaveh Razavi ETH Zurich

†Equal contribution joint first authors

Abstract-DDR5 has shown an increased resistance to Rowhammer attacks in production settings. Surprisingly, DDR5 achieves this without additional refresh management commands, pointing to the deployment of more sophisticated in-DRAM Target Row Refresh (TRR) mechanisms. This paper reverse engineers such advanced TRR schemes in DDR5 devices for the first time. Our findings show that compared to older mitigations deployed in DDR4, these new schemes have considerably fewer blind spots spread over many refresh intervals. This means that an effective DDR5 Rowhammer pattern must precisely track thousands of refresh operations, which we show is not possible with existing techniques. To address this challenge, our new DDR5 Rowhammer attack, called Phoenix, self-corrects the pattern whenever it detects a missed refresh operation during the attack. Our evaluation shows that Phoenix triggers bit flips on 15 out of 15 DDR5 devices in our test pool. Using these bit flips, we build the first Rowhammer privilege escalation exploit that obtains root on a commodity DDR5 system with default settings in as little as 109 seconds. These results provide further evidence that a principled Rowhammer mitigation, such as per-row activation counters, is mandatory for a secure operation of future devices.

## 1. Introduction

Four years after its inception, DDR5 devices remain protected against Rowhammer attacks. Recent work shows that this protection is due to improved Target Row Refresh (TRR) mechanisms inside commodity DDR5 chips [1], [2]. What remains unclear is how these mechanisms manage to capture aggressor rows in advanced Rowhammer patterns [3], [4], [5]. Our reverse-engineering efforts show that significantly longer Rowhammer patterns are nowadays necessary to bypass these new protections. To trigger Rowhammer bit flips, such patterns need to remain in-sync with thousands of refresh commands, which is challenging. Our new Rowhammer attack, called *Phoenix*, resynchronizes these long patterns as necessary to trigger the first DDR5 bit flips in devices with such advanced TRR protections.

Rowhammering DDR5. In 2024, Zenhammer [6] reported the first Rowhammer bit flips on one of ten tested DDR5 DIMMs. These initial DDR5 results are surprising, given that earlier work using similar patterns could trigger bit flips on 40 out of 40 DDR4 DIMMs [3]. An improved DRAM substrate could explain the increased resilience of DDR5 devices against Rowhammer, but recent work shows that the DDR5 substrate is similarly vulnerable to

Rowhammer as DDR4 devices [1]. Another possibility could be the introduction of the new Refresh Management (RFM) commands for DDR5 devices to give the device more time to perform internal mitigative refreshes, but neither CPUs from Intel nor AMD send any RFM commands under Rowhammer workloads [2]. In the absence of RFM commands and improvements to the DRAM substrate against Rowhammer, all indications point toward improved in-DRAM TRR mechanisms in DDR5 chips [1].

TRR mechanisms in DDR5. Our FPGA-based reverse engineering experiments on DDR5 devices from SK Hynix, currently the largest DRAM vendor [7], [8], reveal that compared to DDR4 [3], [4], [5], these new TRR mechanisms change their behavior over significantly longer periods of activity — sometimes thousands of refresh intervals. This change makes it challenging to apply the state-of-theart reverse engineering technique that looks at individual activate commands due to this significant increase in TRR's state [5]. Instead, we devised a new reverse-engineering technique that allows studying the TRR behavior at the granularity of refresh intervals. Using this technique, we can zoom out to identify less frequently sampled refresh intervals among many thousands of them, and thereafter, zoom in to analyze the precise TRR behavior at these specific intervals with previous techniques [3], [5]. This approach enables us to study these new and more complex TRR mechanisms in DDR5 for the first time. Our results based on reverse engineering two particular TRR mechanisms show that a significant portion of activations in specific refresh intervals are not accounted for by the TRR mechanisms.

Bypassing TRR mechanisms on DDR5. We leverage our reverse-engineering results to build Rowhammer patterns that evade the TRR mechanisms on these DDR5 devices. These carefully crafted patterns, covering 128 and 2608 refresh intervals, hammer particular activation slots in very specific refresh intervals only. As a result, they evade the corresponding TRR mechanisms. Furthermore, these patterns need to be aligned with the right refresh command to be effective, which we optimize by hammering multiple banks simultaneously. We show that executing these new complex patterns triggers bit flips on all 10 SK Hynix DDR5 RDIMMs in our test pool. However, executing these patterns from commodity systems requires reliable synchronization with the refresh command over thousands of refresh intervals.

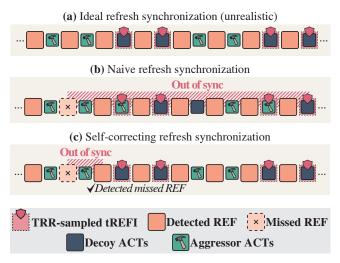

Phoenix. We find that the state-of-the-art synchronization

method [6] misses refresh commands regularly, making it unsuitable for effective Rowhammer attacks on DDR5. We explore two techniques for a more effective synchronization in the design of *Phoenix*, the first system-level Rowhammer attack that bypasses advanced TRR schemes deployed in DDR5 devices. The first technique aims to improve refresh detection by separating Rowhammer accesses and refresh synchronization accesses into different threads. Instead of improving refresh detection, the second technique aims to detect a missed refresh and resynchronize the pattern accordingly. Our results show that while the first technique improves the state of the art, it still fails to remain synchronized for a sufficiently large number of refresh intervals, preventing Phoenix from triggering bit flips. However, the second technique, which we refer to as self-correcting synchronization, can keep Phoenix synchronized with refresh commands for entire refresh windows, sufficient for our new patterns to trigger bit flips.

We evaluate Phoenix on 15 DDR5 UDIMMs produced between 2021 and 2024. Phoenix triggers bit flips on all these devices in seconds. We use Phoenix to craft the first end-to-end DDR5 page table exploit that succeeds in as little as 109 seconds. Our measurements show that increasing the refresh rate by  $3 \times$  mitigates Phoenix on devices we tested while introducing an overhead of 8.4% in the SPEC2017 benchmark suite [9].

Contributions. We make the following contributions:

- We reverse engineer two distinct TRR implementations in DDR5 devices from SK Hynix using a series of carefully crafted experiments.

- We derive custom Rowhammer patterns that effectively bypass TRR mechanisms on these devices based on the insights from our reverse engineering.

- We present Phoenix, a new Rowhammer attack that leverages a new self-correcting refresh synchronization mechanism to execute these new Rowhammer patterns.

- We show that Phoenix triggers bit flips on all 15 DDR5 devices in our test pool. We use these bit flips to craft the first Rowhammer privilege escalation exploit on a commodity DDR5 system with default configuration.

Responsible disclosure and open sourcing. We started a responsible disclosure of Phoenix through the Swiss NCSC with SK Hynix, CPU vendors, and major cloud providers on June 6, 2025. The issue remained under embargo until September 15, 2025. We were informed on September 12 that there is a BIOS update for AMD client machines to address the issue, but we could not independently verify if this update adequately addresses Phoenix. Phoenix is tracked under CVE-2025-6202. More information, including the source code for all the experiments and the exploit, can be found at the following URL: https://comsec.ethz.ch/phoenix

## 2. Background

We discuss DRAM organization (§2.1) and operation (§2.2), followed by changes in DDR5 (§2.3). We then provide background on the Rowhammer vulnerability (§2.4) and the proposed mitigations (§2.5).

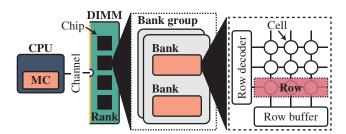

**Figure 1. DRAM organization.** The hierarchical organization of a modern DRAM system such as DDR5 DIMMs.

## 2.1. DRAM Organization

A dynamic random-access memory (DRAM) system, such as a DDR5 Dual In-line Memory Module (DIMM) or *device*, is organized hierarchically (Fig. 1). At the bottom, DRAM *cells* store single bits of information in capacitors. Matrices of cells are arranged in *rows* and *columns*, forming a *bank*. Each bank has a row decoder to select a row, transferring the entire row to the row buffer, and a column decoder to select specific columns for access. Banks are grouped into *bank groups* within a DRAM *chip*. A DDR5 DRAM module typically has two *subchannels*, each with multiple DRAM chips operating in lockstep mode and organized into *ranks*. DIMMs are connected to the CPU's memory controller through dedicated memory *channels*.

Server systems typically use Registered DIMMs (RDIMMs) instead of Unbuffered DIMMs (UDIMMs), which include an on-DIMM buffer to reduce the electrical load on the memory controller. As RDIMMs are designed for servers, most of them are equipped with rank-level Error Correction Code (ECC) in addition to On-Die Error Correction Codes (ODECC) in the DDR5 DRAM chip itself.

## 2.2. DRAM Operations

The memory controller (MC) communicates with a DDR5 DRAM device by following the DDR5 protocol [10], which specifies DRAM commands and their required timings.

**Memory Operations.** When accessing data, the MC issues an activate (ACT) command to the DRAM row given by the memory address. The activation loads the row bits into the row buffer, from which data can be read (RD) or written (WR) by specifying the requested column. After an access, precharge (PRE) prepares the bank for the next ACT.

**Periodic Refreshes.** The capacitors in DRAM cells leak charge over time, which would lead to retention errors. To avoid such errors, the MC issues a REF command every refresh interval (tREFI, i.e., 3.9 µs on average).

## 2.3. Changes introduced in DDR5

With DDR5, several changes were introduced to the DRAM architecture and protocol, of which we briefly summarize the ones relevant to our work.

Higher Refresh Rate. DDR5 devices require refresh commands to be sent once every 3.9 µs on average by default, which is two times more often than on DDR4 (7.8 µs).

Refresh Management. The Refresh Management (RFM) command provides additional time to the DRAM device to refresh memory cells, thus protecting data integrity during periods of high memory activity (e.g., Rowhammer). This device-specific, optional feature requires MC support and may not be required by all DDR5 DIMMs. RFM is based on per-bank counters that track the number of activations, and whenever a certain threshold is reached, the MC issues an RFM to reduce the counter and perform a mitigative refresh. Recent work [2] showed that RFM is not used by the memory controllers of AMD Zen 4, Intel Alder Lake, and Intel Raptor Lake CPUs.

#### 2.4. Rowhammer

Rowhammer is a DRAM disturbance error that was first publicly reported in 2014 on DDR3 [11]. Rowhammer allows an attacker to flip bits in DRAM *victim* rows by repeatedly activating neighboring *aggressor* rows. A multitude of attacks have demonstrated the practicality of exploitation with Rowhammer to cause denial-of-service [12], escalate privilege [13], [14], [15], [16], [17], [18], [19], leak data [20], [21], [22], [23], degrade deep learning models [24], [25], [26], and attack VMs [27], [28], browsers [29], [30], [31], [32], [33], and systems across the network [34], [35].

**Hammer Count.** The Hammer Count (HC) refers to the cumulative number of activations to aggressor rows. Accordingly, the *minimum* HC (HC $_{\rm min}$ ) is the lowest HC to trigger a bit flip in a DRAM row, which varies across different rows. Therefore, the HC $_{\rm min}$  characterizes a device's Rowhammer vulnerability level [36]. Generally, smaller technology nodes make DRAM cells more vulnerable to Rowhammer by reducing the HC $_{\rm min}$ , for example, from 138.4K–314K in DDR3 to 20K–80K in DDR4 across different vendors [36].

DDR5 DRAM is equipped with ODECC, which increases the  $\mathrm{HC_{min}}$  as its error correction capabilities need to be bypassed prior to observing any bit flips. Gloor et al. [1] were the first to measure the  $\mathrm{HC_{min}}$  over 128 rows of two DDR5 RDIMMs from Samsung and Micron by suppressing REFs using a custom fault injector. They found that both devices have a lowest  $\mathrm{HC_{min}}$  of around 32K, which is similar to DDR4 devices. Therefore, they attributed the increased Rowhammer resistance to improved mitigations.

**Patterns.** Various access patterns have been shown to trigger Rowhammer [4], [16], [36], [37], [38], [39]; however, the most effective one remains the *double-sided* pattern, which activates two aggressor rows on either side of the victim row [28]. To bypass in-DRAM Rowhammer mitigations, state-of-the-art *non-uniform* patterns hammer different aggressors of a pattern more or less often [3], [30] while using *decoy* rows [40] to trick the mitigation from sampling those rows instead of the aggressors. For the first time, *Zenhammer* [6] reported bit flips on DDR5 DIMMs using non-uniform patterns, but only on one of ten tested DIMMs.

**Refresh Synchronization.** SMASH [29] showed that carefully placing NOPs in between hammering sequences affects REF scheduling, which can help in bypassing TRR mitigations more effectively. Later, Blacksmith [3] adopted this idea by explicitly detecting REFs using the bank-conflict

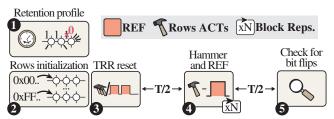

Figure 2. U-TRR experiment. After profiling DRAM rows, U-TRR resets the TRR and waits for half of the retention time, T/2. Then, it executes a hammering-refreshing payload. Finally, after the remaining retention time has passed, it checks for bit flips.

side channel before executing each round of its non-uniform patterns, greatly increasing the number of effective patterns and bit flips. More recently, Zenhammer [6] proposed a new *continuous* and *non-repeating* refresh synchronization method that works more reliably on AMD systems and avoids the need for flushing rows during synchronization.

## 2.5. Rowhammer Mitigations

There have been many proposals for mitigating Rowhammer in software [14], [18], [34], [41], [42], [43], [44], [45], [46], [47], inside the MC [11], [48], [49], [50], [51], [52], [53], [54], [55], [56], [57], [58], and more recently, inside DRAM itself [40], [59], [60], [61], [62], [63], [64], [65], [66], [67], [68]. Despite these proposals, DRAM vendors rely on proprietary TRR mitigations, whose mechanism are undisclosed. At the very high level, TRR tries to detect aggressor rows in its sampler, and proactively refresh the victim rows during the available slack in the standard refresh commands. Earlier work on DDR4 [3], [4], [5] proved that these TRR mitigations are insecure and can be bypassed.

Reverse Engineering TRR. Previous work reverse-engineered aspects of DDR4 TRR implementations by using the bit flips themselves as a side channel [3], [4]. For example, researchers determined how frequently REFs perform TRR by (i) disabling refreshes, (ii) hammering half of  $\mathrm{HC_{min}}$ , (iii) issuing a single REF, and (iv) hammering for the remaining half of  $\mathrm{HC_{min}}$ . If no bit flips occurred, the issued REF must have been a TRR [4]. As this method involves hammering for  $\mathrm{HC_{min}}$  times, it may affect the TRR mechanism and conceal observing the actual behavior.

Alternatively, U-TRR [5] relies on retention errors as a side channel for detecting TRRs activity, as shown in Fig. 2. To run an experiment, U-TRR first identifies adjacent rows with similar retention times (1). It then initializes victim and aggressor rows obtained from the profiling with a data pattern (2) and resets the TRR-internal state by hammering dummy rows (3). After waiting for half of the retention time, U-TRR hammers aggressor and dummy rows for multiple rounds, while issuing REFs to give TRR opportunities to refresh the victims (4). Finally, after the remaining retention time of the profiled rows has passed, U-TRR checks the victims for bit flips (5).

Although recent work shows that RFM is not deployed on recent CPUs with DDR5 [2] and the hammer count is similar compared to DDR4 despite ODECC, there have

**Table 1. DDR5 RDIMMs.** For each DIMM of the major DRAM manufacturer SK Hynix [8], we report its manufacturing date (Mf. Date); size; data transfer rate (Speed); device width (Wd.); and DRAM geometry as number of ranks (RK), bank groups (BG), banks per bank group (BA), and rows (R).

| ID             | Mf. Date<br>[Yr-Mth] | Size<br>[GiB] | Speed<br>[MT/s] | <b>Wd.</b> [b] | <b>Geometry</b><br>#(RK,BG,BA,R) |

|----------------|----------------------|---------------|-----------------|----------------|----------------------------------|

| $H_0$          | 2023-04              | 64            | 4800            | x4             | $2, 8, 4, 2^{16}$                |

| $H_1$          | 2023-04              | 64            | 4800            | x4             | $2, 8, 4, 2^{16}$                |

| $H_2$          | 2023-04              | 16            | 4800            | x8             | $1, 8, 4, 2^{16}$                |

| $H_3$          | 2023-04              | 64            | 4800            | x4             | $2, 8, 4, 2^{16}$                |

| $H_4$          | 2023-07              | 32            | 4800            | x8             | $2, 8, 4, 2^{16}$                |

| $H_5$          | 2023-10              | 16            | 4800            | x8             | $1, 8, 4, 2^{16}$                |

| $H_6$          | 2024-02              | 16            | 4800            | x8             | $1, 8, 4, 2^{16}$                |

| $H_7$          | 2024-02              | 32            | 4800            | x4             | $1, 8, 4, 2^{16}$                |

| $H_8$          | 2024-05              | 32            | 4800            | x8             | $2, 8, 4, 2^{16}$                |

| H <sub>9</sub> | 2024-08              | 32            | 4800            | x8             | $2, 8, 4, 2^{16}$                |

been no reports of DDR5 bit flips on more recent DDR5 devices. This suggests that the TRR mechanisms must have improved substantially. This raises the fundamental question: are today's DDR5 DRAM devices still vulnerable to Rowhammer?

# 3. Overview of Challenges

We aim to understand how the newly deployed TRR mechanisms on DDR5 devices operate. Rigorously analyzing these mechanisms allows us to assess their ability to prevent Rowhammer attacks. This is our first **challenge** (1.):

**★**(C1.) Understand how in-DRAM TRR mechanisms on current DDR5 DIMMs operate.

In §4, we present the first analysis of TRR mechanisms on DDR5 devices. Due to the complexity of current TRR implementations, we devise a reverse engineering methodology to look at the TRR behavior across tREFIs rather than at individual ACTs. Our analysis covers two DIMMs from SK Hynix (H<sub>2</sub>, H<sub>6</sub> in Tbl. 1), currently the largest DRAM vendor [7], [8]. The results show that the state of their TRR sampling mechanisms is large: the sampling occurs irregularly and repeats after hundreds (H<sub>2</sub>) or even thousands (H<sub>6</sub>) of tREFIs. Nevertheless, our experiments expose less frequently sampled tREFIs on both DIMMs, revealing opportunities to hide activations from TRR.

Given these exploitable tREFIs, our next goal is to build Rowhammer patterns that can bypass TRR. These patterns also allow us to easily cross-test other devices from the same vendor without having to reverse engineer their TRR mechanisms first. This motivates our second challenge:

**†** (C2.) Leverage the insights from reverse engineered TRR mechanisms to build effective Rowhammer patterns.

In § 5, we present our new TRR-avoiding Rowhammer patterns that are fully compliant with the JEDEC DDR5 timings [10]. Our patterns are carefully designed to only hammer in selected tREFIs in patterns that consist of 128 (H<sub>2</sub>) and 2608 (H<sub>6</sub>) tREFIs. Our FPGA evaluation on 10 RDIMMs shows that they are *all* vulnerable to these patterns and that these patterns are highly effective in triggering bit flips.

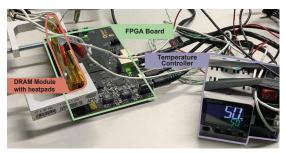

**Figure 3. FPGA testing setup with heating infrastructure.** The Antmicro DDR5 Tester board [69] with the MaxWell FT200 [70] PID controller and custom-size DRAM heater pads.

However, requiring precise synchronization for thousands of refresh intervals immediately raises concerns regarding their feasibility on commodity systems. Furthermore, it is unclear if the same TRR mitigations deployed on RDIMMs are also present on UDIMMs. This leads to our last challenge:

**i.** (C3.) Ensure the new Rowhammer patterns remain synchronized over thousands of refresh commands to trigger bit flips in a commodity system.

In § 6, we show how our FPGA patterns can be ported to commodity systems. Our analysis of the state-of-theart refresh synchronization [6] method shows that it is unable to remain synchronized with a large number of refresh commands. To address this challenge, our new DDR5 Rowhammer attack, called Phoenix, relies on *self-correcting* refresh synchronization that realigns the pattern execution if it detects missed REFs. Our evaluation in § 7 using a commodity system with a default configuration shows that self-correcting refresh synchronization enables Phoenix to successfully trigger bit flips on all 15 SK Hynix UDIMMs from our test pool. We also demonstrate the practical impact of Phoenix by crafting the first end-to-end DDR5 page table exploit that succeeds in as little as 109 seconds.

# 4. Reverse Engineering TRR

In 2024, Zenhammer [6] reported the first Rowhammer bit flips on only one of ten tested DDR5 DIMMs, whereas earlier work with similar patterns triggered bit flips on all 40 tested DDR4 DIMMs [3]. These state-of-the-art fuzzers generate access patterns that span at most 16 tRefis [3], [6]. This choice is motivated by the assumption that TRR's internal sampling behavior repeats every 16 tRefis, which we refer to as *sampling period*. Given that the susceptibility to Rowhammer ( $HC_{min}$ ) is similar between DDR4 and DDR5 DRAM [1], we hypothesize that TRR in recent DDR5 devices may have increased the sampling period to make it harder to bypass it. Determining this period is the first step in understanding how to craft a successful hammering pattern. This poses our first **question** ( $\mathbf{Q}$ ):

**Q**(Q1.) After how many tREFIS does the sampling behavior of TRR repeat?

To answer this question, we first *zoom out* in § 4.1: instead of tracking individual ACT commands, we profile TRR activity at refresh-interval granularity to identify the

Figure 4. Zooming-out experiment on H<sub>2</sub>.

sampling period. Once this period is known, we examine whether certain tREFI intervals inside the period are sampled less often than others. We call these sparsely monitored regions *light intervals*. This motivates our second question:

$\mathcal{O}(Q2.)$  Within one sampling period, which tREFI intervals are sampled least frequently by TRR?

Having pinpointed the light intervals within a sampling period, in § 4.2 we *zoom in*: we switch our focus to per-ACT granularity, issuing controlled activation sequences exclusively inside a chosen light interval. By observing which activations TRR samples within such a tREFI and which ones it overlooks, we identify which aggressor ACTs can be consistently placed in blind spots that TRR *never* considers. This brings us to our last question:

$\mathcal{O}(Q3.)$  Inside a light interval, can activations be crafted in a way that evade TRR's per-ACT sampling?

**Platform.** For all our RDIMMs experiments, we use Antmicro's RDIMM DDR5 Tester [71]. This FPGA-based memory controller allows us to issue DRAM commands and disable automatic refreshes. The platform keeps a *refresh counter* of the REFs issued since boot, which we use in our experiments. Although we initially faced reliability issues, we resolved them by investing significant debugging effort—including using a high-speed oscilloscope to find bugs in the FPGA's design—so the platform now operates stably for our studies. In Appx. A, we briefly summarize the interesting bugs that we found and are now fixed in the platform's official repository. We also attach a thermocouple sensor with two heater pads around the DDR5 RDIMM, and we use a MaxWell FT200 [70] PID controller to maintain a DRAM temperature of 50°C during our experiments.

**Methodology.** Similar to the methodology used by previous work on DDR4 [5], we use retention errors as a side channel to infer if rows have been refreshed by TRR. This side-channel allows us to study the TRR behavior for a profiled set of rows after executing a given experiment-specific *DRAM payload*. We implemented the same approach as summarized in § 2.5 on top of the Antmicro platform.

## **4.1. Zooming Out On** H<sub>2</sub>

We address Q1 in this zooming out stage of our reverseengineering methodology. We start with a candidate length of 16 trefi intervals—matching the period assumed by stateof-the-art fuzzers—and incrementally increase this length until the sampling period becomes evident. For each tested

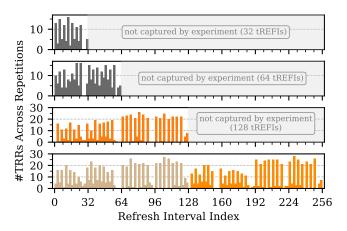

**Figure 5. Zooming out.** The result of brute-forcing the TRR sampling period over 32, 64, 128, and 256 tREFIS, presented using a bin size of 2. We show how often every refresh interval (x-axis) is targeted by TRR over 25 experiment repetitions (y-axis). We can see a repeating sampling behavior in the 256 tREFIS plot.

length N, we carefully craft a DRAM payload spanning exactly N consecutive tREFI intervals as described next.

**DRAM payload.** Each of the N intervals in our payload is monitored by a distinct canary row, i.e., we need Ncanaries in total. We perform double-sided hammering in each interval: we repeatedly activate the two canary-adjacent rows above and below and then issue one REF before moving to the next interval. All canaries are retention-profiled rows with similar retention times as required by the retentionerror side channel. The resulting access pattern, depicted in Fig. 4, is standard-compliant, following the JEDEC DDR5 timing parameter [10]. Once the payload has been executed, we check every canary for retention errors. The experiment is designed such that if a canary survives its hammered tREFI without any retention errors, we can assume that it must have been refreshed by TRR. As the probability that our canary is target of its periodic refresh is negligibly small (once per tREFW, i.e., 1/8192 REFs), we can safely assume that survived canaries were always refreshed by TRR.

Analyzing REF counters. For each experiment, we record the REF counter immediately after the interval. A single run therefore yields a set of REF counter values identifying the TRR-sampled tREFIs. For each candidate period N, we repeat the experiment for 25 times. After every run, we take each recorded REF counter modulo N and map all observations into an N-slot histogram. If N matches TRR's true sampling period, the histogram should reveal a stable pattern: certain tREFI intervals collect many samples (i.e., are frequently monitored) while others are sampled less often (light intervals). We note that if our candidate period M is larger than the true sampling period N, we expect to see a repeating pattern.

**Results.** We perform the experiment for every candidate N from 16 to 256 and present the cases  $N \in \{32, 64, 128, 256\}$  in this order in Fig. 5. The first two cases, already covering up to four times more than the 16-trefi window assumed by current fuzzers [3], [6], show no visible regularity. A clear structure appears only at N=128: where a clear

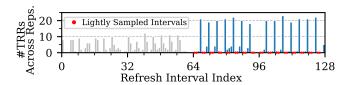

**Figure 6. Zooming in: lightly sampled intervals.** We focus on the last 64 trefis (blue) of the 128-trefi period determined in Fig. 5. This region contains intervals where fewer TRRs happen. We study these lightly sampled intervals (red dots) to identify how often TRR samples them.

Figure 7. Zooming-in experiment on  $H_2$ .

recurring pattern of four blocks becomes visible. Doubling the candidate length N to 256, lets the same pattern reappear in the upper 128-trefi slice (128–255), confirming that it repeats every 128 trefi intervals. This answers Q1 and is our first **observation** ( $\textcircled{\bullet}$ ):

$\odot$  (O1.) TRR on H<sub>2</sub> operates with a sampling period of 128 tREFI intervals.

# **4.2. Zooming In On** $H_2$

To gain a deeper understanding of TRR's sampling strategy, we must study how sampling works within the 128-tREFI sampling period (Fig. 6). In the first 64 tREFIS, no consistent sampling pattern is observable. The last 64 tREFIS, however, exhibit a pronounced regularity: in every group of four consecutive refresh intervals, TRR samples most in the fourth interval, less in the third, and almost never in the first two intervals. We focus on these first two lightly sampled tREFIs (see Fig. 6), of which there are 32 in total. Their low sampling probability makes them an attractive target for hammering aggressor rows. However, before hammering, we need to understand sampling in these intervals better as TRR still samples these intervals occasionally. We now zoom in on each lightly sampled tREFI and profile its behavior at ACT granularity. The goal of this fine-grained analysis is to pinpoint the exact activation slots that TRR samples in this specific interval. Investigating this, will answer Q3.

**Profiling ACTs.** To measure TRR's per-activation sampling across *all* lightly sampled intervals, we craft a DRAM payload that spans over a whole 128-tREFI period. This payload is illustrated in Fig. 7. Prior to the experiment execution, we issue REF commands until the internal refresh counter is aligned with the start of the sampling period, so the 32 lightly sampled tREFIs appear at identical offsets in every run. We issue 59 ACTs in each light interval to the rows adjacent to a fixed set of 59 canaries that we have profiled before. Thus, every light interval activates the same

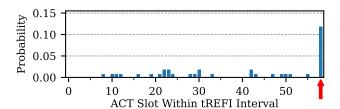

**Figure 8. Zooming in: ACT-based analysis.** We show for each possible activation slot (x-axis) inside the lightly sampled tREFI intervals (y-axis), the probability that TRR samples it. We can see that the last slot (58) is sampled significantly more often than the others, which is why we avoid hammering it.

aggressors in the same order. The remaining 96 intervals are filled with continuous hammering of a double-sided, fixed decoy aggressor pair. By monitoring which canaries TRR refreshes, we reveal the exact activation slots inside each light interval that are sampled by TRR.

**Results.** We execute the 128-tREFI payload 100 times and, for every activation slot (0-58), record how often the corresponding canary is refreshed. Dividing these counts by 100 yields the empirical refresh probability per slot. Each run also issues 128 REF commands from the *regular refresh schedule*, and—because TRR samples the lightly-sampled intervals only infrequently—refreshes from this schedule introduce a non-negligible bias. With a refresh window of 8192 REF commands, the chance that a slot is refreshed by the regular schedule in a single run is  $1/8192 \approx 0.012 \,\%$ . Over 100 runs this baseline accumulates to  $1-(1-1/8192)^{100} \approx 1.2 \,\%$ .

We subtract this 1.2% baseline from the measured probabilities to isolate TRR's contribution. The data reveal a single, pronounced spike at slot 58 (Fig. 8), suggesting that TRR almost exclusively samples the *last* ACT issued before the next REF while ignoring earlier activations within a lightly sampled interval.

**◆**(O2.) In lightly sampled intervals, TRR samples the last issued ACT before the next REF.

We now know which tREFIs in the 128-tREFI sampling period are rarely sampled by TRR. We also know which activation slots to avoid—or fill with decoys—should those intervals be sampled. With this information, we can build effective TRR-bypassing patterns for H<sub>2</sub>, which we present in § 5.

#### 4.3. Generalization & Summary

Our results raise the question if our observations also apply to other DIMMs (i.e., models) from the same vendor. Answering this can help to assess if deployed TRR implementations are the same across different DIMMs, which would mean that they are also vulnerable to the same Rowhammer patterns. To this end, we applied the same methodology on H<sub>6</sub> from SK Hynix (Tbl. 1) and found that the TRR implementation is different. We refer to Appx. B for the details of our findings, which we summarize in Tbl. 2. As we will show later (§ 5.3), the TRR implementations of these two DIMMs already cover all our ten DDR5 RDIMMs.

Table 2. Summary: reverse engineering. We summarize the key findings from our DDR5 reverse-engineering experiments. We report the sampling period, the  $\mathrm{HC}_{\mathrm{min}}$  over all tested rows, and the measured refresh window size.

|                         | SK Hynix H <sub>2</sub>        | SK Hynix H <sub>6</sub>      |

|-------------------------|--------------------------------|------------------------------|

| Sampling Period [trefi] | 128                            | 2608                         |

| tREFW Size [trefis]     | 11054                          | 16582                        |

| HCmin [min/max/avg]     | $(56.6/150.4/105.1)\mathrm{K}$ | $(29.3/70.3/51.4)\mathrm{K}$ |

In the next section (§ 5), we will use these findings to build custom Rowhammer patterns that bypass the TRR mechanism. However, to better understand the time constraints and device vulnerability when hammering these patterns, we need to first determine the refresh window (tREFW) size and the minimum hammer count of our two DDR5 DIMMs.

**tREFW Size.** Previous work [5, §6.1.3] showed that the treff size of one of the devices is smaller than half of the typically assumed size (i.e., 8192 REFs). We replicate this experiment on our DIMMs and find that the treff size is 11054 and 16582 REFs for DIMMs  $H_2$  and  $H_6$ , respectively. This is  $1.3\times$  and  $2.0\times$  more than commonly assumed. This is to the benefit of the attacker as it allows hammering for longer before the targeted row is refreshed.

$\bigcirc$  (O3.) The periodic row refresh of H<sub>2</sub> and H<sub>6</sub> is  $1.3 \times$  and  $2.0 \times$  larger than 8192 REFs (tREFW), respectively.

In § 4.2, we assumed tREFW  $=8\,192$  when calculating the baseline REF probability. For window size W, the per run probability that the regular schedule refreshes a slot is 1/W. Hence, over 100 runs the baseline refresh probability is  $1-(1-1/W)^{100}$ . With  $W=11\,054$  this is  $\approx 0.90\,\%$  (vs.  $1.2\,\%$  for  $W=8\,192$ ). Considering this adjustment results in a similar figure to Fig. 8: a single spike at slot 58 and near zero elsewhere.

$HC_{min}$ . We determine the minimum hammer count ( $HC_{min}$ ) of our two DIMMs over four data patterns (0x0, 0xff, 0x33, 0xcc) following the existing methodology [36]. We report in Tbl. 2 the minimum, maximum, and average combined over all four patterns. The minimum is about in the same range as the minimum numbers reported for different DDR4 DIMMs, between 20K and 80K [36].

$\odot$  (O4.) The HC<sub>min</sub> of our DIMMs, H<sub>2</sub> and H<sub>6</sub>, is in the same range as for modern DDR4 devices.

## 5. Bypassing TRR from the FPGA

Based on the insights from §4, we now build memory access patterns that defeat TRR. §5.1 introduces two patterns,  $\mathcal{P}_{128}$  and  $\mathcal{P}_{2608}$ , based on the reverse-engineered DIMMs,  $H_2$  and  $H_6$ . §5.2 characterizes these patterns, laying the groundwork for running them on commodity systems. §5.3 evaluates the patterns across all our SK Hynix RDIMMs, demonstrating that every tested device is vulnerable.

Experimental Setup. During all experiments and while hammering, the memory controller issues one REF command every tREFI (3.9 µs). All access patterns respect the JEDEC DDR5 timing constraints [10]. Before each run, aggressor

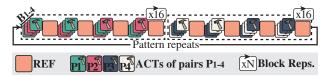

Figure 9. Hammering pattern for DIMM  $H_2$ .

| Algorithm 1: SK Hynix pattern (H <sub>2</sub> ), 128 tREFIS.          |             |  |  |  |  |  |  |

|-----------------------------------------------------------------------|-------------|--|--|--|--|--|--|

| 1 <b>for</b> $i = 1 \dots 16$ <b>do</b> 2 HAMMER_REF(decoys, 4 tREFI) | ⊳ 64 trefis |  |  |  |  |  |  |

| 3 for $i = 116$ do 4 HAMMER_REF(aggressors, 2 tREFI)                  | ⊳ 64 trefis |  |  |  |  |  |  |

| 5 HAMMER_REF(decoys, 2 tREFI)                                         |             |  |  |  |  |  |  |

rows are initialized with random data and their corresponding victim rows with the bitwise inverse.

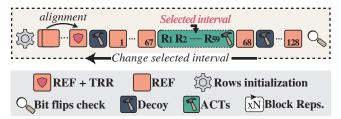

#### 5.1. Rowhammer Patterns

Both patterns combine two interval types revealed by the reverse-engineering analysis in § 4. In a *light* interval, we hammer the aggressor pair for nearly the entire tREFI. Immediately before the next REF, we issue a decoy access as TRR appears to focus its sampling on the last activation (§4.2). In all other intervals, we hammer a fixed double-sided decoy row pair.

**Pattern**  $\mathcal{P}_{128}$  (H<sub>2</sub>). We showed that every 128 tREFIs contain a 64-tREFI period with 32 lightly sampled intervals (§ 4.1). The pattern  $\mathcal{P}_{128}$  aligns with this sequence: the four-interval block is executed 16 times to cover the 64-tREFI window. The remaining 64 tREFIs are sampled more frequently, and therefore, we access only a fixed decoy pair. The pattern is visualized in Fig. 9 and described in Alg. 1.

**Pattern**  $\mathcal{P}_{2608}$  (H<sub>6</sub>). The pattern  $\mathcal{P}_{2608}$  takes the same approach as  $\mathcal{P}_{128}$  to hammer in lightly sampled intervals only. However, because of its longer pattern length—2608 tREFIS —the pattern's structure is more complex. The pattern is described in detail as pseudocode in Alg. 2.

#### 5.2. Pattern Characterization

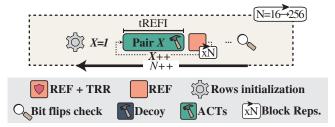

As shown in §4.1, TRR does not sample every tREFI interval in the same way. Our Rowhammer patterns therefore are effective only at specific refresh-counter offsets. On an FPGA, we can issue extra REF commands to align the counter with the offset before hammering the pattern. A commodity CPU lacks this capability, so we enumerate all vulnerable offsets to estimate the probability that a run starting at an arbitrary REF lands at a vulnerable offset.

**Vulnerable offsets.** To identify the refresh-alignment offsets at which a pattern triggers bit flips, we scan the entire refresh counter range modulo the pattern length. At each offset, we hammer up to 1024 rows in the current bank and stop as soon as a bit flip is observed; if any bit flips, we record the offset as vulnerable and advance to the next one. This procedure is repeated for every bank to check whether the set of vulnerable offsets is bank-specific or shared.

#### **Algorithm 2:** SK Hynix pattern (H<sub>6</sub>), 2608 tREFIS.

```

1 for k = 1 ... 8 do

D 1288 trefis

for j=1\dots 5 do

2

HAMMER_REF(decoys, 5 tREFI)

HAMMER_REF(aggressors, 3 tREFI) ▷ light interval

4

5

HAMMER_REF(decoys, 24 tREFI)

6

HAMMER_REF(decoys, 1 tREFI) ▷ Shift after 160 tREFIs

7

HAMMER_REF(decoys, 16 tREFI)

D 1288 trefis

for k = 1 \dots 8 do

9

for j = 1 ... 5 do

10

HAMMER_REF(decoys, 21 tREFI)

11

HAMMER_REF(aggressors, 3 tREFI) ▷ light interval

12

HAMMER_REF(decoys, 8 tREFI)

HAMMER_REF(decoys, 1 tREFI) ▷ Shift after 160 tREFIS

13

14 HAMMER_REF(decoys, 16 tREFI)

```

**Table 3. Pattern characteristic: refresh alignment.** For each pattern, we report the number of vulnerable refresh alignment offsets; and the probability to start hammering at one of them both without and with our pattern optimization.

|                                    | $\mathcal{P}_{128}$ (H <sub>2</sub> ) | $\mathcal{P}_{2608}$ (H <sub>6</sub> ) |

|------------------------------------|---------------------------------------|----------------------------------------|

| <b>#Vulnerable Refresh Offsets</b> | 2/128                                 | 92/2608                                |

| Hit Probability [%]                | 1.56                                  | 3.53                                   |

| Hit Probability Optim. [%]         | 24.96                                 | 56.48                                  |

**Results.** Sweeping all 128 REF offsets on  $H_2$  with  $\mathcal{P}_{128}$  and all 2608 offsets on  $H_6$  with  $\mathcal{P}_{2608}$  yields two insights. First, vulnerable alignments are sparse: 2 of 128 for  $H_2$  and 92 of 2608 for  $H_6$ . Second, the same offsets recur in every bank. Tbl. 3 summarizes the counts and the probability to hit a vulnerable refresh alignment.

$\bullet$  (O5.)  $\mathcal{P}_{128}$  has 2/128 vulnerable REF offsets (i.e., 1.56%), while  $\mathcal{P}_{2608}$  has 92/2608 (i.e., 3.53%); in both cases, the same offsets recur in every bank.

**Pattern optimizations.** As our patterns need to be aligned to certain vulnerable REF offsets, we optimize the pattern execution to increase the chance of hitting a vulnerable offset. In essence, we run four shifted instances of the pattern on *each* of four banks in parallel, thus increasing the success chance by a factor of 16. This is illustrated in Fig. 10 and explained in more detail in Appx. C.

**●** (**O6.**) We can increase the chance of hitting a vulnerable REF offset by running four shifted instances of the pattern in parallel on each of the four banks.

Activation rate vs. hammer duration. Besides the refresh alignment, the effectiveness of our hammering patterns is limited by the number of activation commands we can issue to aggressors in a tREFI. Commodity CPUs may achieve a lower activation rate than FPGAs because of the cacheflushing overhead and memory-controller scheduling [6]. Therefore, we want to *estimate* how much slack our patterns permit by reducing the number of aggressor ACTs per tREFI.

We sweep over 1024 victim rows in a randomly selected bank at a refresh alignment previously identified as vulnerable. Within each hammered tREFI, we issue 30, 40, or 50 ACTs to the aggressor rows; and fill the remaining slots of the 59 ACTs/tREFI with decoy accesses, whereas non-hammered tREFIs contain only decoys. The pattern is

Figure 10. Optimized  $\mathcal{P}_{128}$  pattern. We hammer four shifted pattern instances on each of four banks in parallel to increase the chance of hitting a vulnerable REF offset by a factor of 16.

Figure 11. Activation rate vs. hammering duration. We show for different activation budgets (ACTs/tREFI) and hammering durations (#tREFWs), the share of rows (%) with at least one bit flip.

applied for one to five consecutive tREFWs since §4.3 shows that rows are refreshed less often than once per tREFW.

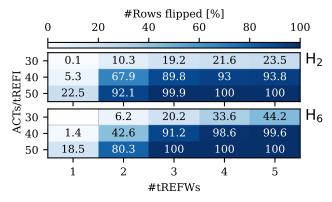

**Results.** Fig. 11 shows the share of rows that incur at least one bit flip when we hammer  $\mathcal{P}_{128}$  on  $H_2$  and  $\mathcal{P}_{2608}$  on  $H_6$ , sweeping the activation budget (30–50 ACTs/tREFI) and the hammering duration (1–5 tREFWs) over 1024 victim rows in a randomly selected bank.

Even with a slack of almost 50% in the activation budget (30 ACTs/tREFI), both patterns still flip rows: after five tREFWs, 23.5% of the rows flip on  $H_2$  and 44.2% on  $H_6$ . Raising the budget to 40 ACTs/tREFI markedly increases the success rate: three tREFWs already flip 89.8% ( $H_2$ ) and 91.2% ( $H_6$ ) of the rows, and four tREFWs exceed 93% for both devices. At the highest budget, 50 ACTs/tREFI, nearly all rows flip within two tREFWs and full (100%) row coverage is achieved after three tREFWs. Given these results, we will focus in future experiments on the more efficient range, i.e., between 40 and 50 ACTs/tREFI.

**©** (O7.) Even with a reduced activation budget of 30–40 ACTs/trefi, both  $\mathcal{P}_{128}$  on H<sub>2</sub> and  $\mathcal{P}_{2608}$  on H<sub>6</sub> induce bit flips when the pattern is synchronized to a vulnerable REF offset and executed for several consecutive trefws.

**Discussion.** We attribute the continuing rise of flipped rows across successive tREFWs to two effects. First, a row is most vulnerable when hammering starts immediately after its periodic refresh, providing the longest time to hammer. Extending the hammering duration makes it increasingly likely that every row eventually encounters this worst-case point in the refresh cycle. Second, ODECC does not write back corrected data to DRAM when reading from memory. Hence, a bit that flips in one tREFW will persist in the next one. If a second bit flips in the same ECC word, the

Table 4. DDR5 RDIMMs: pattern coverage and effectiveness. For each DIMM, we report the average  $\mathrm{HC}_{\mathrm{min}}$  and the percentage of rows with at least one bit flip when hammering the pattern for one up to five refresh windows (trefws).

| ID    | $\mathrm{HC}_{\mathrm{min}}$ | Pat                            | terns                | trefws / Flipped Rows [%] |      |       |       |       |  |

|-------|------------------------------|--------------------------------|----------------------|---------------------------|------|-------|-------|-------|--|

|       | [x1000]                      | $\overline{\mathcal{P}_{128}}$ | $\mathcal{P}_{2608}$ | 1                         | 2    | 3     | 4     | 5     |  |

| $H_0$ | 108.4                        | 1                              | Х                    | 6.4                       | 63.7 | 86.2  | 95.1  | 96.6  |  |

| $H_1$ | 99.2                         | 1                              | X                    | 13.6                      | 86.6 | 98.9  | 99.8  | 100.0 |  |

| $H_2$ | 105.1                        | 1                              | X                    | 22.5                      | 92.1 | 99.9  | 100.0 | 100.0 |  |

| $H_3$ | 98.3                         | 1                              | X                    | 19.2                      | 93.3 | 99.9  | 100.0 | 100.0 |  |

| $H_4$ | 114.0                        | 1                              | X                    | 4.9                       | 53.6 | 77.1  | 88.6  | 93    |  |

| $H_5$ | 51.6                         | X                              | 1                    | 13.3                      | 82.4 | 99.3  | 99.9  | 100.0 |  |

| $H_6$ | 51.4                         | X                              | 1                    | 18.5                      | 80.3 | 100.0 | 100.0 | 100.0 |  |

| $H_7$ | 93.6                         | 1                              | X                    | 21                        | 91.4 | 99.4  | 99.7  | 100.0 |  |

| $H_8$ | 104.4                        | 1                              | X                    | 14.4                      | 86.3 | 98.2  | 99.6  | 99.8  |  |

| $H_9$ | 52.7                         | X                              | ✓                    | 3.6                       | 63.9 | 97.3  | 99.9  | 100.0 |  |

Pattern  $\mathcal{P}_{128}$  originates from DIMM  $H_2$  and  $\mathcal{P}_{2608}$  from DIMM  $H_6$ .

scheme's single-bit error-correction capability is exhausted and the error becomes visible at the memory controller.

**●** (**O8.**) Bit flips can accumulate over hammering multiple tREFWs before they become visible.

## 5.3. Cross-Device Evaluation

We apply our two custom Rowhammer patterns to the SK Hynix DDR5 RDIMMs listed in Tbl. 1. For every module, we rerun the vulnerable offset experiment for each pattern to determine whether the module is susceptible to one or both patterns. Any DIMM that exhibits at least one vulnerable offset is then tested for its effectiveness: starting from an identified offset, we sweep 1024 randomly chosen rows and record how many experience at least one bit flip. We hammer the aggressor rows for 50 ACTs/tREFI, while varying the hammering duration for one to five tREFWs.

**Results.** Tbl. 4 summarizes the cross-device evaluation. Every DIMM responds to exactly one of the two patterns:  $\mathcal{P}_{128}$  triggers bit flips on seven modules, whereas  $\mathcal{P}_{2608}$  is effective on the remaining three. When the selected pattern is aligned with a vulnerable REF offset and executed at 50 ACTs/trefi, it reaches near-complete coverage in just a few refresh windows: after three treffws, eight of the ten modules already show bit flips in at least 97.3% of the 1024 probed rows. Extending the hammering to five treffws raises the minimum coverage to 93% across all modules, with seven modules achieving 100%.

These results reveal that SK Hynix deploys, at most, two functionally distinct TRR implementations in the DDR5 generation from 2021 to 2024 (see Tbl. 1). Thus, reverse engineering only a handful of modules is sufficient to craft patterns that generalize to the entire product line.

**©**(**O9.**) All our 10 SK Hynix RDIMMs share the same TRR mitigation as  $H_2$  (7×) and  $H_6$  (3×).

**Relation to HC**<sub>min</sub>. We determine the  $HC_{min}$  of our RDIMMs, in the same way as we already did in § 4.3 for DIMMs  $H_2$  and  $H_6$ . The result in Tbl. 4 reveals that there is a connection between the pattern's length (i.e., TRR

implementation) and the  $HC_{\min}$  of the DIMMs. Devices with a hammer count lower than 51.4K (i.e.,  $H_5$ ,  $H_6$ ,  $H_9$ ) trigger bit flips only with the longer  $\mathcal{P}_{2608}$  pattern, whereas those with a hammer count of at least 93.6K are vulnerable to the shorter  $\mathcal{P}_{128}$  pattern.

$\odot$  (O10.) DIMMs with a lower avg.  $HC_{\min}$  require longer patterns to bypass TRR, whereas DIMMs with a higher avg.  $HC_{\min}$  can be attacked with shorter patterns.

# 6. Bypassing TRR in Commodity Systems

In our FPGA-based evaluation, we had full control over the DRAM commands. A key novelty of our patterns is that they are longer and need to be repeated over many thousands of refresh intervals. This is crucial to bypass TRR as missing a REF will lead to hammering our aggressors too late and erroneously detecting a REF will lead to hammering them too early. Unlike on the FPGA, where we can control the REF commands to synchronize, on commodity systems we have no control over when REFs are issued and need to detect REFs to synchronize our pattern execution with them.

▲ Assumption. Having full control over the REF commands to synchronize our pattern execution.

To eliminate this assumption, we first define the requirements of the refresh synchronization method (§ 6.1) and evaluate the state-of-the-art method by Zenhammer (§ 6.2). As this method cannot satisfy our requirements, we propose two novel methods to improve the reliability of detecting REFs (§ 6.3) and to self-correct the pattern's execution whenever we lose synchronization (§ 6.4).

**Platform.** All our system-level experiments are run on an AMD Zen 4 (R7 7700X) system running on Ubuntu 20.04 with GNU/Linux kernel 5.15.0.

**Oscilloscope.** We analyze our experiments using McSee [2], an oscilloscope platform capable of capturing and decoding the DDR5 protocol. This setup is based on a DDR5 interposer sitting in between the memory controller and the DIMM, and a software pipeline for decoding the captured traces. Equipped with this, we can precisely study when REFs happen to assess the quality of our REF synchronization method and correctness of our hammering pattern.

# 6.1. Requirements Analysis

Our patterns rely on precise synchronization with REF commands to ensure hammering specific tREFIs only. This requirement is not new as previous work [3], [6], [29], [30] already employed synchronization. However, they synchronized the pattern once per pattern hammering repetition only [3], which is insufficient for the significantly longer patterns that can trigger bit flips on DDR5 devices. Given the intricate nature of such patterns that hammer at very specific refresh intervals, we *must* synchronize with *every* tREFI. Furthermore, since these patterns hammer on comparably fewer refresh intervals inside the patterns, they need to remain synchronized with REFs for longer durations to reach a desired HC. Finally, due to tREFI being halved on DDR5 (compared to DDR4), these patterns need to

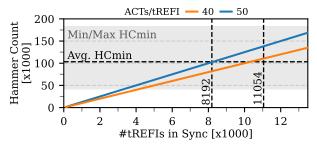

Figure 12. Required #tREFIs in sync for pattern  $\mathcal{P}_{128}$ . We show the hammer count (y-axis) achievable with a number of tREFIs in sync (x-axis). Each line represents a different activation rate (ACTs per tREFI). The  $\mathrm{HC_{min}}$  values are based on the three DIMMs vulnerable to  $\mathcal{P}_{128}$ , see § 5.3. We show the tREFW according to the standard (8192) and as measured (11054) in § 4.3.

synchronize with REF commands twice as often, Therefore, we need a synchronization method that detects REFs with high reliability. Before evaluating the existing method, we analyze for how long our pattern needs to stay in sync.

We aim to answer the following question: how many trefis do we need to stay in sync when hammering our pattern to trigger any bit flips? For the calculation, we consider the  $\mathcal{P}_{128}$  pattern and the average  $HC_{\min}$  of 103.3 K, based on the three DIMMs vulnerable to this pattern (§ 5.3). As we visualize in Fig. 12, we need an activation rate of at least 50 ACTs/tREFI to reach the average HC<sub>min</sub> within a trefw (i.e., 8192 REFs). The  $\mathrm{HC}_{\mathrm{min}}$  is based on our devices vulnerable to  $\mathcal{P}_{128}$  (see § 5.3). To the attacker's benefit, we determined earlier (§ 4.3) that the tREFW is actually 11054 REFs. This means, we could hammer for longer with a lower rate ( $\approx$  38 ACTs/REF) to reach the same average  $\mathrm{HC_{min}}$ . This trade-off provides us with some flexibility: we can hammer with a lower activation rate in exchange for a more reliable refresh synchronization method. We will explore next if the state-of-the-art refresh synchronization method meets our minimum requirements.

# 6.2. Zenhammer Refresh Synchronization

Our goal is to evaluate how well the state-of-the-art Zenhammer [6] refresh synchronization works and if it allows us to stay in sync sufficiently long to trigger bit flips. Zenhammer's *continuous* and *non-repeating* refresh synchronization method employs precise timing measurements with multiple rows to eliminate "blind spots" and avoid cache flushes.

**Experiment.** We integrate Zenhammer's synchronization method into the code of our  $H_2$  hammering pattern and use it to synchronize with *every* REF. To facilitate the analysis, we access two specific *marker rows* whenever we detect a REF. We run the hammering code on our test platform and capture 50 traces of each 2 ms (i.e., around 25 K trefis) with McSee. As we found that we need an activation rate between 40 and 50 to reach the average  $HC_{\min}$  before a row gets periodically refreshed, we repeat the experiment with both activation rates.

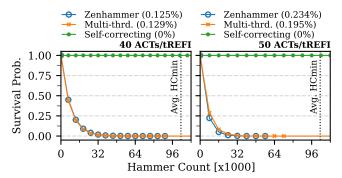

**Results.** In Fig. 13, we show the probability of staying in sync (y-axis) over time, expressed as hammer count (x-axis), for both activation rates in different subplots. We can

Figure 13. Comparison of refresh synchronization methods. We compare Zenhammer's synchronization against a multi-threaded variant of it, and our self-correcting synchronization. We show for two activation rates, the probability of reaching a hammer count (x-axis) given the synchronization's methods error rate (legend). We omit line markers where the probability is below 0.001 %.

see that, with neither 40 nor 50 activations per trefi, the Zenhammer refresh synchronization is reliable enough to stay in sync for the necessary time to reach the average  $\mathrm{HC_{min}}$  of our DIMMs vulnerable to  $\mathcal{P}_{128}$ . In the best case (40 ACTs/trefi), where the error probability is the lowest, we can reach a HC of 35 840, 55 040, and 72 960, before the probability of staying in sync drops below 1 %, 0.01 %, and 0.001 %, respectively. Given the survival probability p of 0.000169 % to reach the average  $\mathrm{HC_{min}}$  of 103.3 K, we would need to repeat hammering the pattern for around 591.7 K times to succeed once, which makes the attack infeasible in practic in practicee.

$\odot$  (O11.) The state-of-the-art refresh synchronization method is insufficient to keep in sync with refreshes for long enough to reach the  $\mathrm{HC}_{\min}$  of vulnerable rows.

**Directions.** Our analysis of many DRAM traces with Zenhammer's refresh synchronization revealed that the most common reason for losing synchronization is because of missing just a *single* REF. If this happens, we hammer the pattern's interval i, although we should have skipped one interval, i.e., hammer the interval i+1 to not get sampled by TRR. Therefore, our goal is to optimize the synchronization method for this single-missed REF case. To tackle this, we came up with two possible directions: (i) improving the reliability of detecting REFs and (ii) realigning the pattern's execution whenever we detect a missed REF. We consider both directions: we propose a new multi-threaded variant of Zenhammer's refresh synchronization (§ 6.3) and a new self-correcting synchronization method (§ 6.4).

## 6.3. Multi-Threaded Refresh Synchronization

We present a multi-threaded variant of Zenhammer's refresh synchronization method [6], aiming to improve the reliability of detecting REFs. This is motivated by the assumption that single-threaded refresh synchronization will inevitably miss a REF at some point. Missing a REF can be caused by, for example, system events such as receiving an interrupt or being preempted by the kernel. The synchronization detection itself can also fail, for example, if another process

accesses the same bank as the one used for synchronization. We propose to separate activations used for hammering from those for synchronizing to increase the reliability of detecting REFs. Therefore, our multi-threaded refresh synchronization uses several synchronization threads that work in parallel on different banks and different cores.

**Approach.** We use three threads, each pinned to a different core and solely responsible for detecting refreshes. A fourth, *main* thread hammers in the pattern's respective intervals and thereafter, checks if the synchronization threads detected a REF. If two out of three threads detected a REF within  $0.12 \mu s$  (3% of tREFI) of each other, we consider the REF as genuine and continue with the pattern's execution.

**Results.** Fig. 13 shows the result of our multi-threaded refresh synchronization method. We can see that for 40 ACTs/tREFI, the error probability is similar to Zenhammer (0.129 % vs 0.125 %). For the case of 50 ACTs/tREFI, the error probability is by 0.039 percentage points lower but still higher than the best case with the Zenhammer method. Given this, we conclude that the refresh synchronization method is not practical to reach the average  $HC_{\rm min}$ .

**●** (O12.) Multi-threaded refresh synchronization only slightly improves the reliability compared to the state-of-the-art method and only at a higher activation rate.

## 6.4. Self-Correcting Refresh Synchronization

Orthogonal to making the synchronization more reliable, we came up with a completely different approach: self-correcting refresh synchronization. The idea is that instead of trying to avoid missing REFs, which seems to be unrealistic to achieve in practice, we accept that we will miss some REFs and instead adjust the pattern execution whenever a REF is missed. The implementation is simple as we already retrieve a timestamp during synchronization that we can use for detecting one or multiple missed REFs.

**Approach.** Our approach for self-correcting refresh synchronization is illustrated in Fig. 14: we show how a perfect refresh synchronization would execute the pattern (a), compared to the naive refresh synchronization (b), and our novel self-correcting refresh synchronization (c).

After detecting a REF, we compare the rdtscp timestamp of the last detected REF with the current timestamp. Based on the difference, we check if we missed any REFs, and if so, how many refresh intervals of the pattern we need to skip to realign the execution. To optimize for the most common case of missing a single REF only, we choose the threshold in a way that we avoid false positives despite REFs sometimes being slightly delayed. For example, given a threshold of  $5.5\,\mu s$  (i.e.,  $1.4\times tREFI$ ), a smaller timestamp difference will be considered as no missed REF and a larger one as *one* missed REF.

**Evaluation.** We repeat the same experiment (§6.2) using our self-correcting refresh synchronization method. We take 50 traces (each 2ms) for each activation rate using our scope. The results in Fig. 13 show that the self-correcting refresh synchronization method makes the overall pattern execution significantly more reliable. From the 9 and 58 missed REFs

**Figure 14. Self-correcting refresh synchronization.** The ideal pattern execution where each REF is correctly detected **(a)** is compared to the execution if one REF is missed **(b-c)**. In the naive synchronization case **(b)**, the execution is continued and remains out of sync, causing the aggressors to be sampled by TRR. With our self-correcting approach **(c)**, we detect the missed REF and skip one or multiple tREFIs to restore the synchronization.

for 40 and 50 ACTs/tREFI, respectively, all of them were detected correctly, and the pattern execution was realigned. This allows us to stay in sync for many thousands of tREFIs, thus easily reaching the average  $\mathrm{HC}_{\mathrm{min}}$  of our DIMMs. As we show later in § 7, our novel self-correcting refresh synchronization method enables us for the first time to trigger bit flips on modern DDR5 DIMMs from commodity systems.

$\odot$  (O13.) Self-correcting refresh synchronization allows us to stay in sync for many thousands of tREFIs, sufficient to reach the average  $HC_{\min}$  of vulnerable rows.

#### 7. Evaluation

In this section, we evaluate Phoenix by answering the following three questions:

- 1) How widely applicable are our patterns across different DDR5 UDIMMs from SK Hynix (§ 7.1)?

- 2) Can our patterns trigger the particular bit flips on DDR5 DIMMs that enable existing attacks (§ 7.2)?

- 3) Is it possible to build an end-to-end Rowhammer exploit on DDR5 DRAM with our patterns (§ 7.3)?

**Experimental Setup** We evaluate our patterns and the end-to-end attack on an AMD Zen 4 (R7 7700X) system with Ubuntu (GNU/Linux 5.15.0) and default BIOS settings. We use the UDIMMs listed in Tbl. 5. Testing these DIMMs with the state-of-the-art Rowhammer fuzzer, Zenhammer [6], did not show any bit flips.

#### 7.1. Pattern Coverage & Effectiveness

We evaluate on how many of our DDR5 UDIMMs our crafted patterns are effective and how many bit flips they can

**Table 5. Evaluation of DDR5 UDIMMs.** For each DIMM, we report its manufacturing date (Mf. Date); size; data transfer rate (Speed); device width (Wd.); DRAM geometry (number of ranks (RK), bank groups (BG), banks per bank group (BA), and rows (R)); and the Rowhammer pattern it is vulnerable to (§ 5). For each DIMM, we sweep its pattern over 256MB of memory and report the number of one-to-zero (1  $\rightarrow$  0) and zero-to-one (0  $\rightarrow$  1) bit flips. We also report the average time to find the first exploitable bit flip in mm:ss format for three Rowhammer attacks: the page table entry (PTE) attack [14], the RSA key attack [27], and the sudo binary attack [15].

| ID                | Mf. Date  | Size  | Speed  | Wd. | Geometry                 | Pattern |                      | Sweep [#bfs.] |         | Attacks [avg. time] |                         |                         |

|-------------------|-----------|-------|--------|-----|--------------------------|---------|----------------------|---------------|---------|---------------------|-------------------------|-------------------------|

|                   | [yyyy-mm] | [GiB] | [MT/s] | wu. | #(RK,BG,BA,R)            |         | $\mathcal{P}_{2608}$ | 1 → 0         | 0 → 1   | PTE                 | RSA                     | sudo                    |

| $H_0$             | 2021-12   | 8     | 4800   | x16 | 1, 4, 4, 2 <sup>16</sup> | /       | X                    | 3 329         | 5 460   | 10s                 | 4 <i>m</i> 57 s         | 80 m 45 s               |

| $\mathrm{H}_1$    | 2022-07   | 16    | 4800   | x8  | $1, 8, 4, 2^{16}$        | 1       | X                    | 2917          | 4 582   | 14 s                | 7m 6s                   | $49  m  37  \mathrm{s}$ |

| $H_2$             | 2022-08   | 16    | 4800   | x8  | $1, 8, 4, 2^{16}$        | 1       | X                    | 2629          | 4 082   | 15 s                | 6m $38s$                | _                       |

| $H_3$             | 2022-12   | 8     | 4800   | x16 | $1, 4, 4, 2^{16}$        | 1       | X                    | 2837          | 4 5 2 6 | 11 s                | 6m~36s                  | _                       |

| ${ m H}_4$        | 2022-12   | 32    | 5200   | x8  | $2, 8, 4, 2^{16}$        | X       | 1                    | 207           | 318     | 2m 55 s             | _                       | _                       |

| $H_5$             | 2022-12   | 32    | 4800   | x8  | $2, 8, 4, 2^{16}$        | 1       | X                    | 3 922         | 5 821   | 11 s                | 4m $17s$                | _                       |

| $H_6$             | 2023-01   | 32    | 4800   | x8  | $2, 8, 4, 2^{16}$        | 1       | X                    | 6 5 9 2       | 9 672   | 7 s                 | 2m 29s                  | $20m\ 19s$              |

| $H_7$             | 2023-01   | 32    | 4800   | x8  | $2, 8, 4, 2^{16}$        | X       | 1                    | 566           | 860     | 39 s                | _                       | _                       |

| $H_8$             | 2023-01   | 32    | 5600   | x8  | $2, 8, 4, 2^{16}$        | X       | 1                    | 156           | 240     | 4m 6s               | _                       | _                       |

| $H_9$             | 2023-01   | 32    | 6000   | x8  | $2, 8, 4, 2^{16}$        | X       | 1                    | 314           | 486     | 2m 17s              | $9m\ 25s$               | _                       |

| $\mathrm{H}_{10}$ | 2023-02   | 32    | 5600   | x8  | $2, 8, 4, 2^{16}$        | X       | 1                    | 304           | 461     | 7m~27s              | $23  m  57  \mathrm{s}$ | _                       |

| $\mathrm{H}_{11}$ | 2024-01   | 16    | 4800   | x8  | $1, 8, 4, 2^{16}$        | X       | 1                    | 12 523        | 18 446  | 6s                  | 1m 19s                  | 12m  41s                |

| $H_{12}$          | 2024-01   | 16    | 4800   | x8  | $1, 8, 4, 2^{16}$        | 1       | X                    | 10833         | 15 917  | 5 s                 | 1m 27s                  | $21m\ 17s$              |

| $H_{13}$          | 2024-04   | 16    | 5600   | x8  | $1, 8, 4, 2^{16}$        | 1       | X                    | 8 520         | 12761   | 5 s                 | 1m 38s                  | _                       |

| $H_{14}$          | 2024-12   | 16    | 4800   | x8  | 1, 8, 4, 2 <sup>16</sup> | Х       | ✓                    | 24            | 19      | 20 <i>m</i> 15 s    | _                       |                         |

trigger. This can show us if the TRR mitigations deployed on RDIMMs and UDIMMs are the same. As our UDIMM test pool covers devices with manufacturing dates between end of 2021 and end of 2024, it will also show us if the mitigation changed over time.

**Methodology.** For each DIMM, we first determine which of the two patterns,  $\mathcal{P}_{128}$  or  $\mathcal{P}_{2608}$ , are effective in bypassing TRR. We then follow the methodology from previous work [3], [4] and *sweep* the effective pattern over the row-equivalent of 256MB of physically contiguous memory and record the number of bit flips. While sweeping, we hammer each row for one second, i.e., for more than 15 trefws.

**Results.** The results of our pattern sweep is presented in Tbl. 5. For each DIMM, we report the effective pattern, and for this pattern, the number of one-to-zero  $(1 \rightarrow 0)$  and zero-to-one  $(0 \rightarrow 1)$  bit flips. Similar as in our FPGA-based evaluation (§ 5.3), we find that every DIMM is vulnerable to exactly one of the two patterns only:  $\mathcal{P}_{128}$  (8×) or  $\mathcal{P}_{2608}$  (7×). Pattern  $\mathcal{P}_{128}$  with 13 050 bit flips on average, is around  $2.62\times$  more effective than the  $\mathcal{P}_{2608}$  pattern with 4 989 bit flips on average. We will see next how these bits flips affect the attack time of existing Rowhammer end-to-end attacks.

#### 7.2. Exploitation Analysis

We now show that the bit flips produced by our patterns enable existing Rowhammer attacks on DDR5 DIMMs by analyzing their exploitability.

**Attacks.** For this exploitability analysis, we consider three existing Rowhammer attacks targeting (i) **PTEs** (Page Table Entries) to craft a memory read/write primitive [14]; (ii) **RSA**-2048 keys of a co-located VM to break SSH authentication [3]; and (iii) the **sudo** binary to escalate local privileges to the root user [3]. We use the Rowhammer attack simulation framework *Hammertime* [72] with our results

from § 7.1 to simulate the attacks based on the required attack-specific bit flip offsets.

**Results.** We present the results in Tbl. 5. For each of the three attacks, we report the average time to trigger the first exploitable bit flip. We can see that all 15 devices are vulnerable to the PTE attack and the average time to trigger the first exploitable bit flip is 2m 36s. For the RSA-2048 attack, 11 of 15 devices (73%) are vulnerable, with an average time of 6m 20s. Although requiring very specific bit flips offsets, the sudo binary attack still works on 5 of 15 devices (33%) with an average time of 36m 55s. We note that in §7.1, we limited hammering to 256MB but it is likely to find the necessary bit flips for the RSA-2048 and sudo binary attack when hammering for longer.

We conclude this section by showing that the exploitable bit flips that we determined can be used to escalate privileges in a real end-to-end attack. As DDR5 introduces ODECC, which could make memory templating more difficult if the attack's target data is not known in advance, such as in the PTE attack, we chose to replicate this specific attack.

## 7.3. End-to-End Exploit

We integrate Phoenix's bit flip primitive into the privilege escalation exploit *Rubicon* [14], which equips the attacker with an arbitrary memory read/write primitive. Flipping a single bit in the Page Frame Number (PFN) field of a PTE, lets the attacker forge PTEs to arbitrarily read/write into memory. Exploitation requires allocating a large buffer of contiguous physical pages, locating a row with an exploitable bit flip, massaging memory so the target PTE resides in that row, and retriggering the flip to complete the escalation.

**Threat model.** We assume a vanilla x86-64 Linux system where the attacker can run code as an unprivileged user. The system uses a DDR5 UDIMM produced by SK Hynix

employing ODECC and TRR with all BIOS defaults and vendor defenses remain enabled.

Physically contiguous memory. To obtain 4MB contiguous memory blocks, we exhaust smaller page block orders to force the buddy allocator to return 4MB blocks at the tail of the allocation. We then release everything except the 8MB at the tail of the allocation, creating a search window of at least one physically contiguous 4MB block. We slide a 4MB probe across this window and use the DRAM addressing functions [6] with bank conflicts to find the block alignment. Accessing each address pair while recording the minimum latency reveals the alignment: when the probe covers the target block, every pair will trigger a row buffer conflict, marking the first page of the contiguous block.

ECC-aware templating. Templating typically fills aggressor and victim rows with complementary byte patterns, but ODECC makes bit flips data-dependent [73]. Therefore, we prime aggressor rows with 0xAAAAAAAAAAAAAAAA and victim rows with a fake PTE value 0x8000000555555027. This surrogate PTE approximates the layout of a Linux 64-bit page table entry, increasing the chance that a flip found during templating can be retriggered later. We repeatedly hammer and read back the victim rows until the first exploitable bit flip emerges.

Memory massaging and exploitation. After identifying a vulnerable cell, our aim is to install a PTE whose PFN differs from the page table's PFN by exactly one flippable bit. Thanks to the 4MB contiguous aligned blocks, we can choose a sibling frame whose PFN is one bit apart from the target PFN. We free this frame, then map a file to back the file with that frame. Using Rubicon's allocator massage primitive [14], we steer the next page-table allocation onto the target frame. Mapping the same file again at a crafted virtual address writes the sibling's PFN into the PTE located at the vulnerable 8-byte slot. Immediately before hammering, we clear that slot in the sibling page to 0x0 and read it back afterward. If it now contains a valid PTE, we have control over a page table page; otherwise we repeat the entire sequence.

**Evaluation.** We test our attack on DIMM  $H_{14}$ . Across ten successful runs, the time-to-exploitation is between 1m 49s and 17m 6s with an average of 5m 19s.

## 8. Discussion

We discuss extending Phoenix (§8.1) and possible mitigation strategies (§8.2).

# 8.1. Extending Phoenix

Phoenix was a high effort project: debugging the Antmicro FPGA took us roughly 1 person-year, reverse engineering H<sub>2</sub> and H<sub>6</sub> took 0.5 person-year, and developing self-correcting refresh synchronization took another 0.5 person-year, totaling 2 person-years. However, we think more work is needed in this important area and discuss some interesting future directions with an estimation of effort.

**Additional DIMMs.** H<sub>2</sub> and H<sub>6</sub> provided a full coverage of DDR5 SK Hynix RDIMMs and UDIMMs in our pool. Fu-

ture devices from this vendor, however, could introduce new TRR mechanisms. In our experience, reverse engineering a new TRR mechanism from the same vendor typically takes a shorter time given similarities in the implementation.

Additional DRAM vendors. We expect reverse engineering devices from other vendors, such as Micron or Samsung, to take roughly the same amount of time as it took us for SK Hynix. It remains to be seen whether additional system-level techniques, beyond self-synchronization, will be necessary to trigger bit flips on a commodity system with DIMMs from these other vendors.

Additional CPU vendors. Phoenix is designed to work on AMD CPUs. Self-synchronization will likely require additional tuning to work on Intel CPUs. Furthermore, triggering bit flips on Intel CPUs requires bypassing the in-CPU pTRR mitigations as shown by McSee [2]. We are not aware of any work that bypasses both in-DRAM and in-CPU mitigations simultaneously.

**Better fuzzers.** Existing Rowhammer fuzzers [3], [4], [6] fail to find the patterns we crafted in this paper. We attribute this to the TRR sampling behaviors that span over much more refresh intervals in DDR5 which makes the search space significantly larger to brute force. Future fuzzers can explore this space more effectively, for example, by focusing on finding blind spots at the granularity of refresh intervals instead of activations. Such fuzzers could benefit from Phoenix's more accurate refresh synchronization capability.

## 8.2. Mitigations

Mitigating Phoenix requires different strategies when considering existing and future DRAM devices, which we discuss here

Increasing refresh rate. Unlike CPU vulnerabilities that can be mitigated via modifications to the microcode, DRAM features a much more rigid execution pipeline that is not amenable to changes after production. Hence, the only possibility to fully address Phoenix in existing systems is via increasing the refresh rate. Our measurements show that increasing the refresh rate by  $3 \times$  mitigates Phoenix on the most vulnerable device at the system level. SPEC2017 benchmark suite [9] shows an overhead of 8.4% due to this increase in the refresh rate in our test system. We would like to point out that there could be more effective patterns than the ones we constructed where increasing the refresh rate by  $3 \times$  may not be sufficient.

**Fine-granularity refresh.** As a response to our responsible disclosure, we were told that a BIOS update for AMD client CPUs has been issued. This BIOS update switches the memory controller's refresh mode to Fine-Granularity Refresh (FGR). FGR increases the refresh rate, but reduces the time allotted to each refresh command [2]. While it remains to be seen how this change affects Phoenix, we do not think that it will provide a strong protection.

**Rank-level ECC.** Rank-level ECC is known to make Rowhammer attacks more difficult in practice. Previous work, however, has shown that it does not stop Rowhammer attacks in both DDR3 [74] and DDR4 [75] server systems.

Investigating an ECC variant of Phoenix would be an interesting direction for future research.

**Future devices.** We strongly recommend against deploying yet another obscure mitigation without a rigorous security analysis in future devices. Instead, the DRAM vendors must deploy TRR mitigations with principled guarantees [40], [60]. The new Per Row Activation Counting specification [76], [77] provides a possibility for implementing such principled mitigations inside DRAM.

## 9. Related Work

We discuss reverse engineering of TRR implementations via FPGAs and system-level attacks that bypass TRR.